该运放的psrr如何提高

图片没显示,补充一下

图片没显示,补充一下

1.提高环路增益

2.增大环路带宽

3.加大输出电容

1.你基准PSR是多少

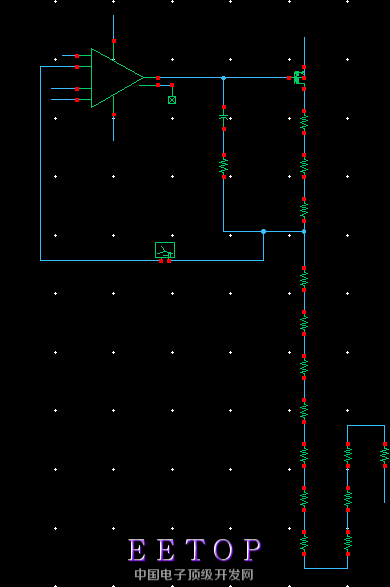

2.运放什么结构

这个PSRR基本可以,如果要提高,可以加大开环增益。

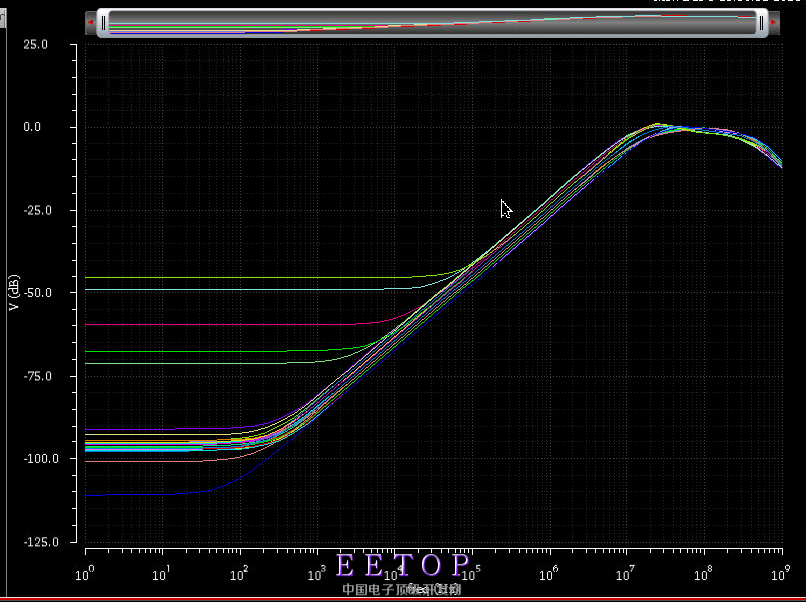

是说基准源的psrr吗?我外部用的是理想源图中那个运放的psrr最低都有-50dB,用的结构是折叠式共源共栅,主要是第二级这里把psrr拉下来了

这个psrr不是接近0了吗?稍微调大了环路增益几个dB,不过最高点的psrr还是没降下来

不过我只把环路增益提高了几个dB,把环路带宽增大了1倍

您好,关键看你要提高哪个频率段的PSRR,别告诉我都要提高。

--------------------------------------------------------------------------------------------

我们是上海漕河泾的芯片设计公司,正在找 芯片测试应用工程师 和 模拟芯片设计工程师

有意可联系 sv@sovan.com.cn

您好,我主要是想将100M这点的psrr降低,希望能达到-10多dB,而现在这个psrr在100M时基本在0dB上。

add a cap at output

I have tried this , but it only reduce the frequency after 100M, the frequency near 100M is still close to 0dB

我尝试过这种方法,不过只改变了100M以后的频率,100M附近的频率还是接近0dB

改变补偿的方式,不要使用米勒补偿,直接在后级pmos gate处加对电源的cap

谢谢指导,最后采用的解决方法,就是在后面的tgate加上一个mos管电容并联mom电容,然后调节下密勒补偿的rc值,可以使得psrr最高点为-4点多dB

同时提高Cc和Cload的值。

Bnadwidth低到远在100M以内。

请问一下小编,你所说的tgate是指功率管的栅端吗?

可以让电压反馈环路的阻抗降低,可以提高高频的PSRR

输出加电容肯定是可以的。明显你加的电容不够大,要么你的LDO是片内的

我想知道小编扫描PSRR的变量是什么?低频的增益看上去掉了很多啊?是扫的电源电压吗?

miller补偿的方式决定了在buffer运放的GBW处的PSR就是接近0或者超过0的。

你把输出改成NMOS管就好了。

补充,输出加电容滤波