三支路电流源续(噪声分析)

有错过前几期内容的同学,请移步到

http://bbs.eetop.cn/thread-617655-1-1.html

本部分主要对三支路电流源的噪声进行简单的分析,说实话,噪声分析还是蛮头大的,不过还是希望通过努力,能够多理解一些。

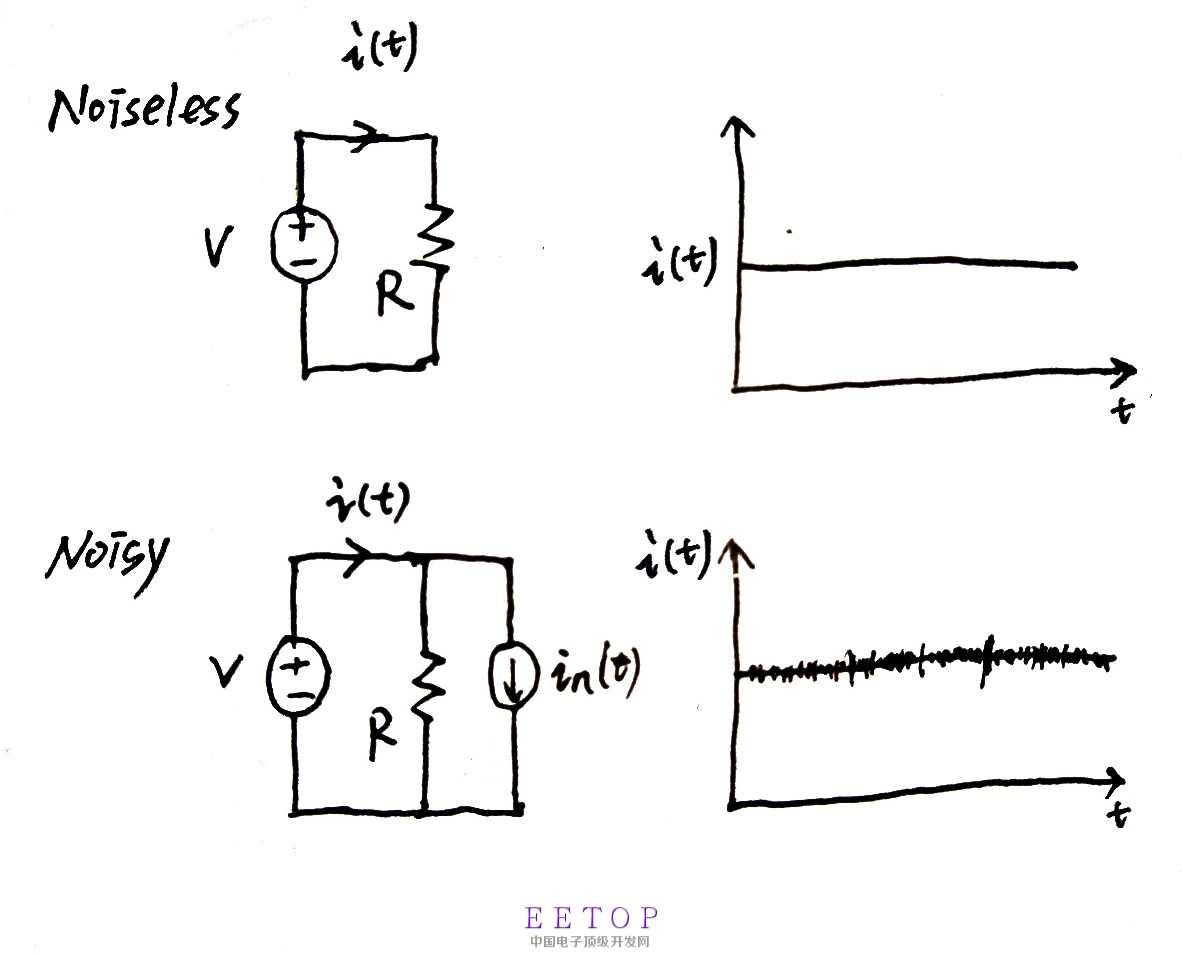

众所周知,噪声是电路中无时无处不在的非理想因素。如图1示意图,对于理想的Noiseless电路,总电流i(t)是理想的,当考虑电阻的噪声后,总电流i(t)和理想值存偏差,对于高性能电路,这个微小的量就需要充分考虑了。

图1

电路中噪声可以用时域或频域的方式表示。

时域上,由于噪声信号的随机特性,无法用瞬态精确表示,通常使用统计学的概率分布表示,如热噪声的瞬态幅值通常满足高斯分布;也可以通过测量噪声的平均功率,用均方根值(RMS)表示。

频域上,噪声的能量用功率谱密度(Power Spectral Density )的形式表示,以1Hz带宽的均方值表示,单位为V^2/Hz,或者表示为V/rt-Hz。

图2

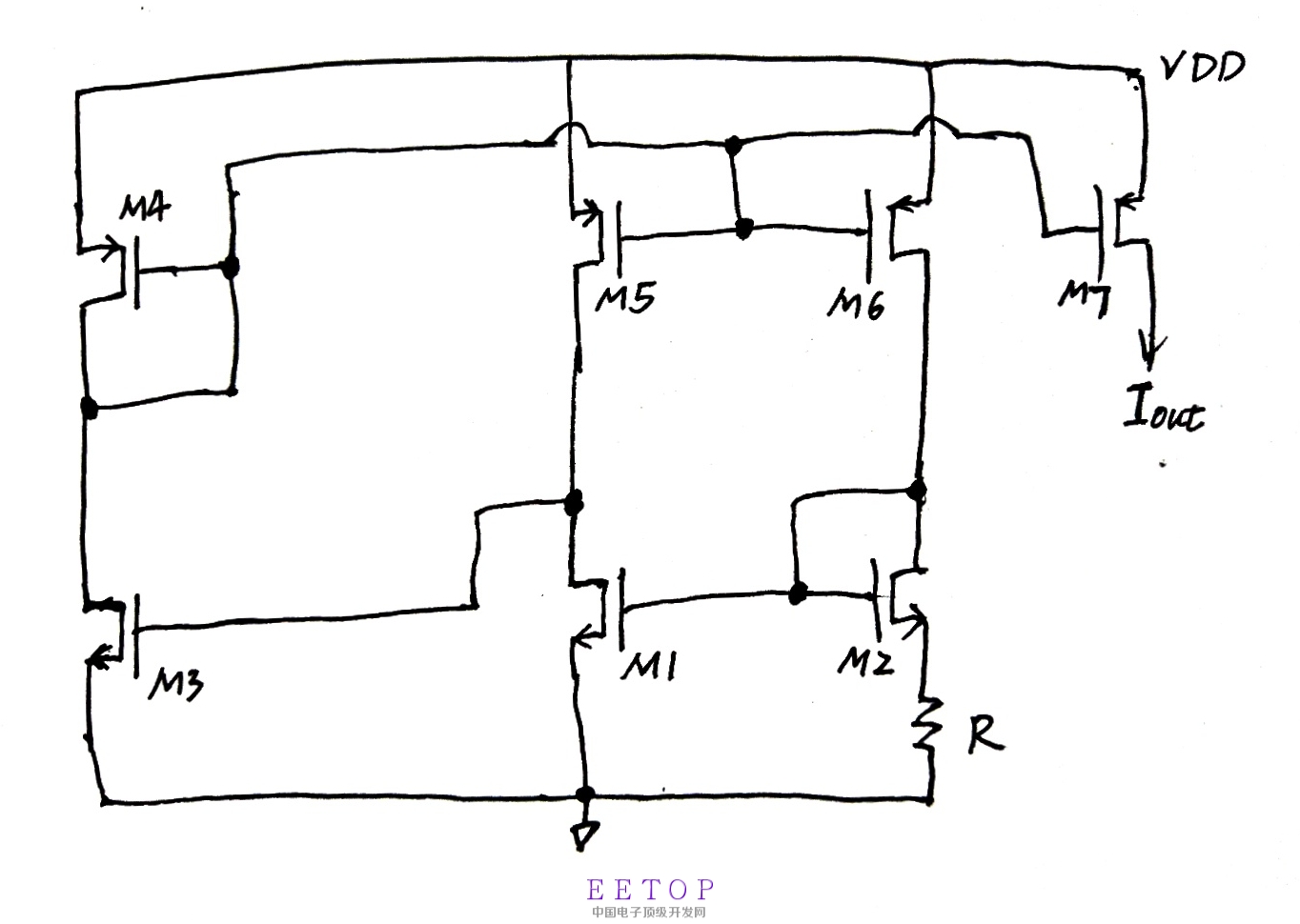

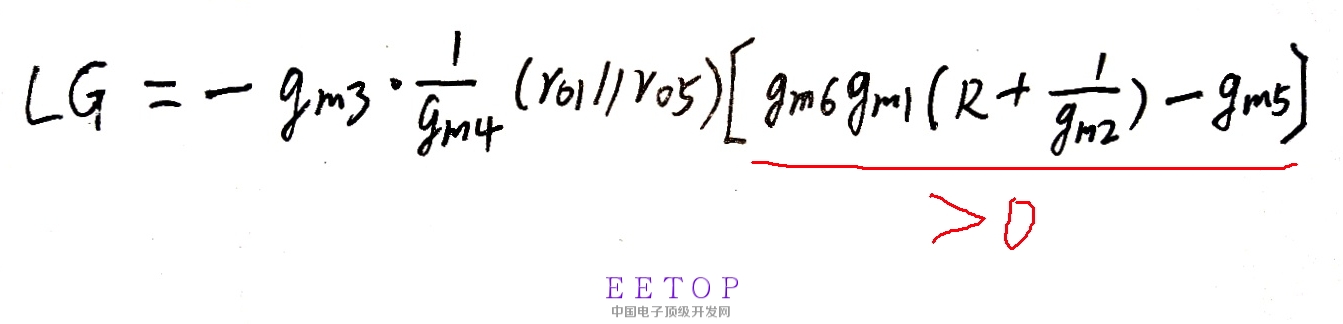

回顾之前图2所示的三支路电流源的分析,其低频环路增益如图3所示,此处暂不做简化,为保证整体是负反馈,图中红色部分应大于0。(注意gm5和gm6是近似相等的)

图3

这里先给出图2的小信号噪声模型,如图4所示,其中输出阻抗仅包含了M1和M5管的ro1和ro5。M1~M7管的噪声表示为栅级的等效电压源(也可以使用并联的噪声电流表示),电阻R的噪声源为VnR。

图4

可以看到,图4中M1~M6和电阻R都是通过节点Vy对输出电流Iout贡献噪声,M7管的噪声则是直接包含在Iout中。

多个不相关噪声源,分别通过不同的传输函数后叠加的表达式如图5 所示。

图5

图4中的各噪声源通过Vy节点对输出电流Iout贡献噪声。首先,可以计算M1~M6管和电阻R到节点Vy的低频增益。

图6

图6举例计算了Vn3和Vn4到Vy的低频增益,同理可以求得Vn1、Vn2、Vn5、Vn6和VnR到Vy的低频增益。

最后给出输出电流与各噪声源的关系如图7。可以看到Vn1~Vn6及VnR经过放大或衰减后,贡献到输出。

图7

化简后,可以得到如图8所示的结果,直觉上,可以看到Vn1、Vn2和VnR的噪声贡献大于Vn3,Vn6的噪声贡献大于Vn5。

图8

好了,这部分内容暂时先写这么多了,下一期,看看能否利用这一节的内容并结合管子的噪声特性,得到输出电流的总噪声。

也请感兴趣的同学,关注一下我的微信公众号,也算是对我的鼓励和鞭策,争取能把更多的和模拟IC设计有关的内容进行分享,扫一扫哟~

前几期胡乱分析了一通,心理也没底,是时候检验一下喽,为验证输出电流的噪声,首先我们搭建如图1的TestBench,输出电流Iout为1uA。

图1

其中电阻R=50KOhms,C=500fF。图中显示了各器件的Dc Operating Points,Stb仿真结果为,环路低频增益32.5dB,Phase Margin为77deg,单位增益带宽为5.6MHz。

为了能够计算图1中输出电流的rms值,需要已知图1中各噪声源的功率谱密度(PSD),从而利用图2计算式,得到的各噪声源到输出电流的PSD。注意,图2的公式是各器件等效到栅级的电压表示噪声源到输出的低频增益。当然实际计算时,也是可以通过转化表示为使用电流噪声源的方式。

图2

基于noise仿真结果,等效各器件噪声电流的root spectral density如图3所示,表示形式为电流谱的形式。

图3

根据图1和图2,可以得到输出噪声功率谱密度,如图4所示。从中也可以看到,各器件的噪声电流源到输出电流的低频增益。

图4

考虑到环路的单位增益带宽为5.6MHz,对图4的电流功率谱密度进行积分,积分区间为0.1Hz~5.6MHz,粗略的积分结果如图5所示。注意此处的积分是按照5.6MHz的噪声带宽(brick-wall filter)。当然该计算结果是偏大的。对输出贡献表较大的器件有M6、R、M1、M2和M5。可以通过减小M6、M1、M2的1/f噪声和热噪声的方式,减小最后贡献到输出的噪声。

图5

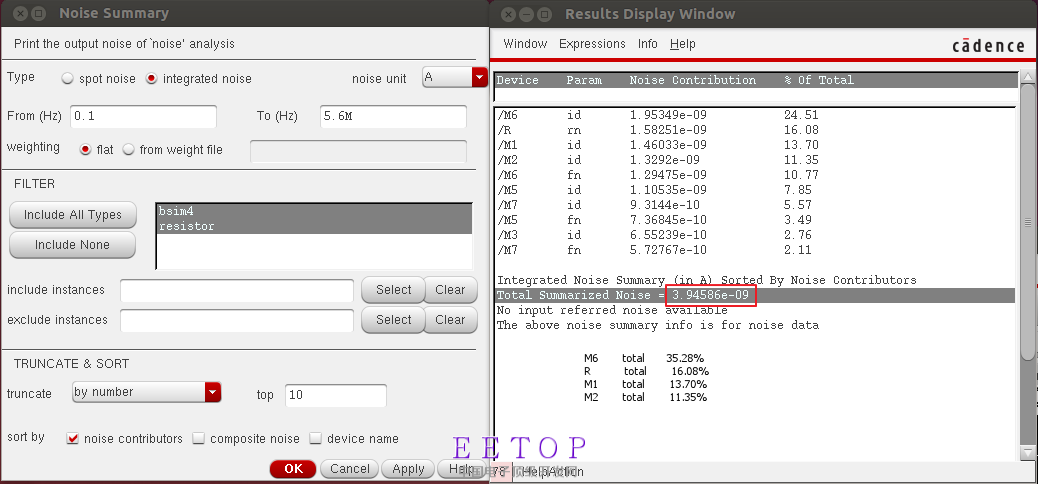

图6为使用EDA仿真结果得到testbench所示电路的noise summary。仿真结果中给出了准确的各器件的噪声共享比例,总的噪声rms值为3.9nA。可以看到图5中粗略计算结果为8.1nA,虽然存在一些偏差,但还是比较接近仿真结果了

图6

此系列(三支路电流源)也算有个阶段性的结束,从中可以体会到,不是很负载的电路,其中能够学到的东西,还是蛮多的。也希望同学们能有所收获吧。

Mark for it