请教---一个从事高速、高精度ADC设计的朋友都可能遇到的问题

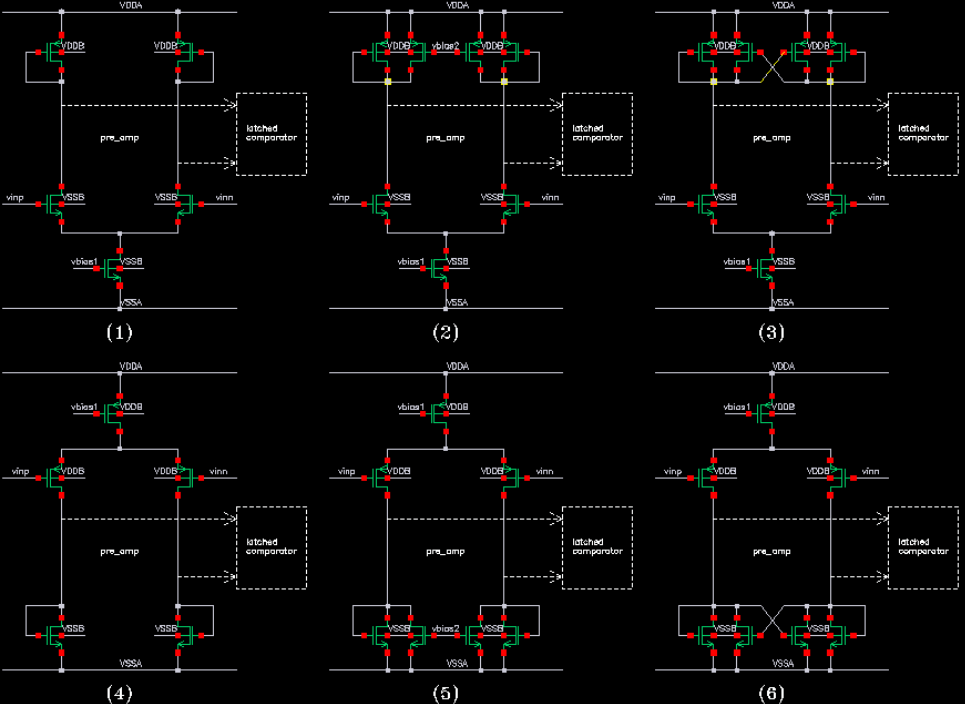

ADC电路实现时,该模块需要关注的指标是:失调+DC GAIN+GBW+传输延迟(总的要求tp<=1ns)+Kickback noise+输入寄生电容+功耗,真诚希望大家针对这几种结构,在这些指标中作出优/劣评判,指点指点。谢谢!

个人觉得,你这也可以说是一种结构。

为什么呢,大同小异

1,2,3是NMOS输入,4,5,6是PMOS输入。

1,2和3无非在增益和速度上有差别。

1,2,3里面,3有增益和速度的优势,但是相应的kickback也会比较大。

如果对kickback什么的特别在意,我觉得用AC coupling可能更好一些。

另外,你这不要reset switch吗?

一点浅见,请高手发言。

To use NMOS or PMOS input depends on the input common mode voltage

(2) is probably best if you want speed

(1) is slow

(3) has positive feedback on the load.But it will also make the swing too large. The positive feedback is not necessary if you already have a latch comparator at the 2nd stage

谢谢2楼和4楼大哥的指点。

如果最大失调不大于+、-30MV,不打算加入RESET结构,因为之前做了一个无源加法器+带RESET的PRE_AMP+LACTHED_COMPARATOR的结构,发现在RESET相负载电容太大了(采用开关电容+比较器的结构),相位余度不够,造成很大的RING,无法完全setteing。

该比较器希望用在五位的量化器中,参考电压3.2V,每个STEP=200MV,整个比较器(2nd_stage LATCHED_COMPARATOR的输入失调电压估计有120MV的量级,折合到输入端的失调电压为120MV / A0,所以希望A0大概可以做到5或6)的最大失调不希望超过+、-90mv。并且希望当+、-10mV信号输入时在1NS之内完成比较;要求KICKBACK噪声不影响各个比较器间的正确比较;输入寄生电容足够小,以减轻前级有源加法放大器的等效负载电容以减少功耗。

故,真诚大家就以上提到的几个指标之间的折中,尤其是输入失调电压谁优谁劣,多多指点!谢谢大家了

sc pre-amp 不加reset,能够用么?

5b flash 看起来是用在sigma-delta ADC?

reset 主要是帮助overdrive recovery.

如果有preamp, kickback 一般都不是问题。

你准备跑多快?

6楼的大哥您好!

确实是希望用在4阶噪声整形5位量化,2MHZ带宽 95DB(预期目标)的Delta-Sgima ADC中。

SC+PREAMP+LATCHED_COMPARATOR结构中,在采样相是把Vrefn-Vcm电压采样到电容上,在比较相在串上有源加法器的输入。

您讲过“reset 主要是帮助overdrive recovery”,能帮忙详细解释一下吗?担心考虑不周到头来导致真个系统崩溃掉啊!肯请大哥不吝赐教!谢谢

之前的RESET结构还有一个功能是AUTOZERO OFFSET的,6楼大哥提到的Overdrive recovery是不是说把preamp输出端的差分电压重新拉到0V呢,是不是可以用一个跨接这两个差分节点开关来实现复位呢?

你时钟跑多块呢?

没有reset 得话,在信号从正的大信号,一下跳道很小的负值的时候,很容易出错。这个是比较器的标准测试之一。

在sigma-delta ADC 情况会好一点,无非就是quantization noise 稍微大点。

呵呵不过如果你的loop 的stability 不太好,这样的错误,就可以trigger oscillation:-)

vdslafe大哥,

你眼力这么精,估计你是行业高手,很感谢您的友情支持!

时钟128MHZ,系统级仿真基本结束,实际带宽可以达到3.2MHZ,SNDR=104DB(模型中包括KT/C噪声),CS1=4.5PF,vin=+2.5~-2.5v。

现在关键是电路级的设计,OTA 的SR GBW都很大,先开始比较器设计。

前文提到的用跨接PRE_AMP输入端的开关来实现overdrive_recovery可行吗?谢谢!

“前文提到的用跨接PRE_AMP输入端的开关来实现overdrive_recovery可行吗?谢谢”

笔误,修订为:

前文提到的用跨接PRE_AMP输出端的开关来实现overdrive_recovery可行吗?谢谢

都是牛人啊

学术贴,顶一下。

呵呵,不错啊

该考虑的都提到了啊

tks 4sahring

tks 4sharing

.......sigma delta 中比较器实在很无所谓了,越简单越好,

10# saiaoying

要求不高的话,可以考虑接一个MOS diode 防止 大输入信号下,preamp的输出swing太大。

输出端接开关也是常用的做法,考虑一下控制时钟,也可以防止一部分kickback。

我倒是感兴趣你的DA怎么做?

中国电子顶级开发网 ( 黑ICP备09056077号)|联系我们|广告事务 |Archiver|WAP| 网站统计

GMT+8, 2010-3-1 07:13, Processed in 0.111013 second(s), 10 queries, Gzip enabled.

中国电子顶级开发网 ( 黑ICP备09056077号)|联系我们|广告事务 |Archiver|WAP| 网站统计

GMT+8, 2010-3-1 07:13, Processed in 0.111013 second(s), 10 queries, Gzip enabled.

为什么呀

research

研究贴,赞一个

研究贴,赞一个

关注一下