pipeline会被sar和sigma delta取代吗

没人来发表一下意见吗

個人觀點:

目前ISSCC Very High Speed Conversion Rate SAR ADC 都是用先進製程(<90nm)才能做到的,

而且100MHz Conversion Rate , 12-bit , 就要一個 1.4GHz的Clock ,

1.4GHz Clock is generated by PLL,對PLL IP來說也不容易,

而且1.4GHz PLL jitter又要小,不然 ADC SNR 會下降.

但ISSCC 都不說ADC Clock要從何而來(PLL),

因為他們在量測ADC時,

Clock都用非常貴的儀器來外灌的(RF Synthesis).

如果是0.13um/0.18um/0.25um/0.35um等成熟製程,

要用SAR ADC做到100MHz Conversion Rate , 12-bit 會非常辛苦.

所以要在Process Technology >90nm以上實現100MHz,12/14-bit還是會用Pipelined ADC比較好實現.

PS : 100MHz Pipelined ADC 只需100MHz的 Clock Source.

async SAR 好像不需要高速时钟?

是的,Async SAR 不需要高速时钟,

但是內部還是要自己跑1.4GHz的Clock,

1.4GHz 一個週期period=0.7nsec,

只有0.13um製程以下的logic gate可以Run在<0.7nsec的Period.

impossible

感谢大牛,确实觉得新工艺使得SAR变得越来越快,而且集成度和功耗也会好一些,还有连续时间sigma delta都是越来越快。不过感觉高速高精度pipeline用.18um就可以实现,成本更低

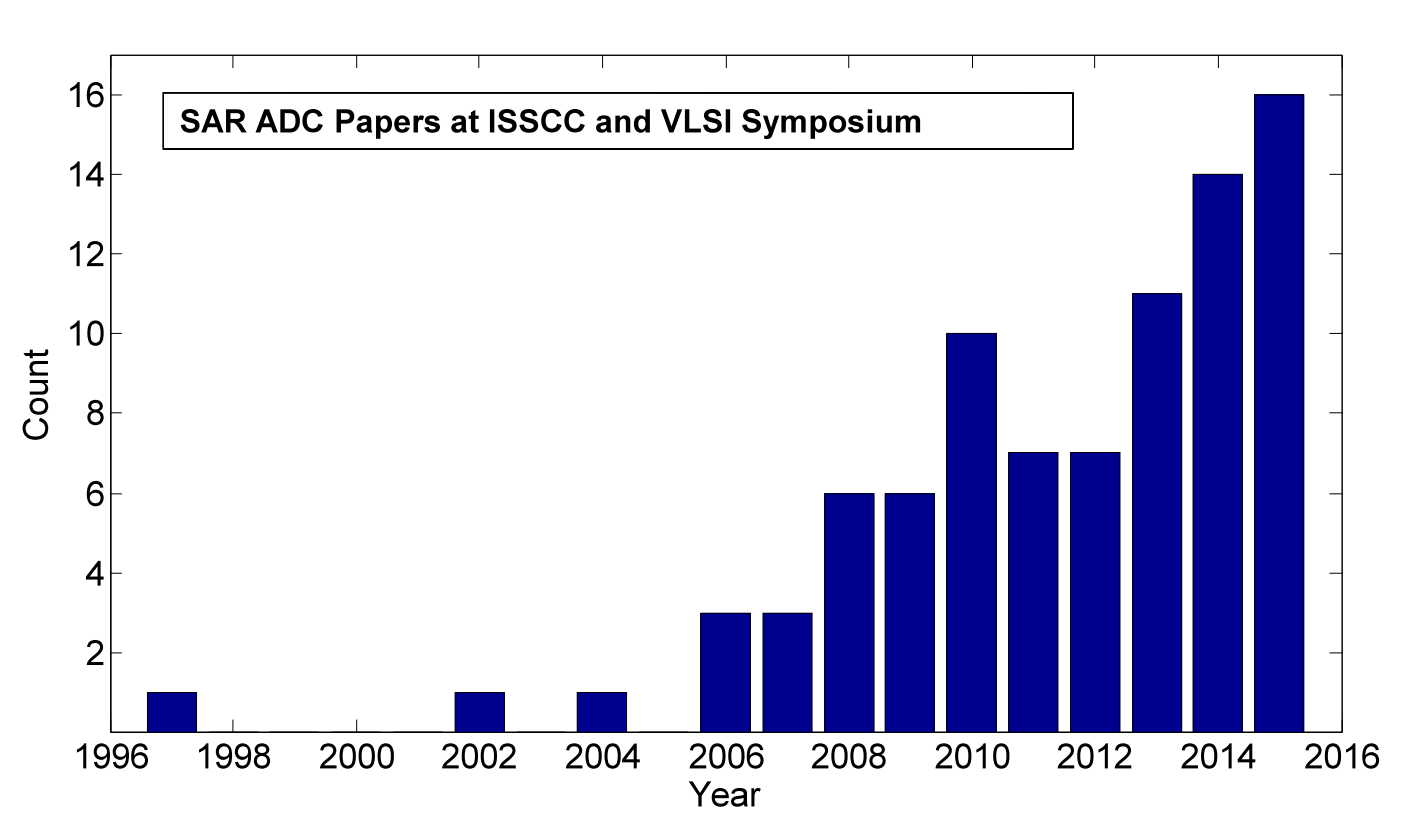

SAR and SD are more popular now

高速sar的片上buffer也不好做

是么,最近调研看的,可能都是为了发文章,感觉性能都很叼

是啊,不知道做pipeline还有没有前途。

我这里也有这个表格,是斯坦福一个教授整理的吧

对大多数模拟信号来说,速度不高,在新工艺下用pipeline会比较浪费,用sar和sd能更好的发掘工艺特性。不过高速是永远的追求啊,pipeline是不会消失的。

工业级的高速高精度应用上还是Pipeline主导, 不计功耗,只追求性能