12b 160M pipeline ADC的 sfdr 只有53dB,求大侠帮忙看看!

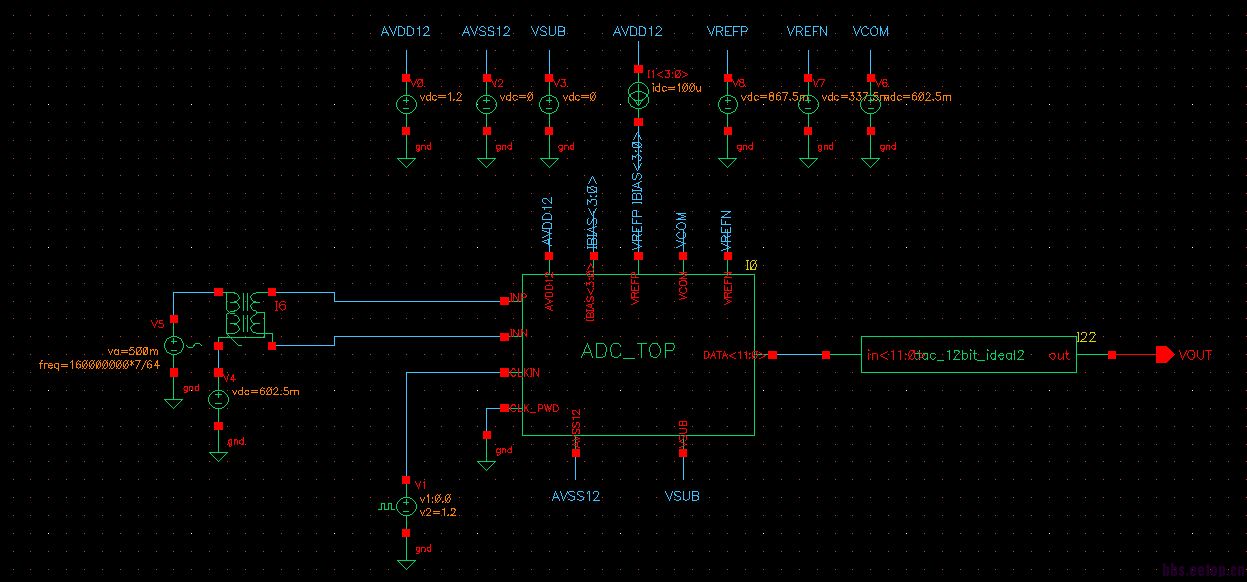

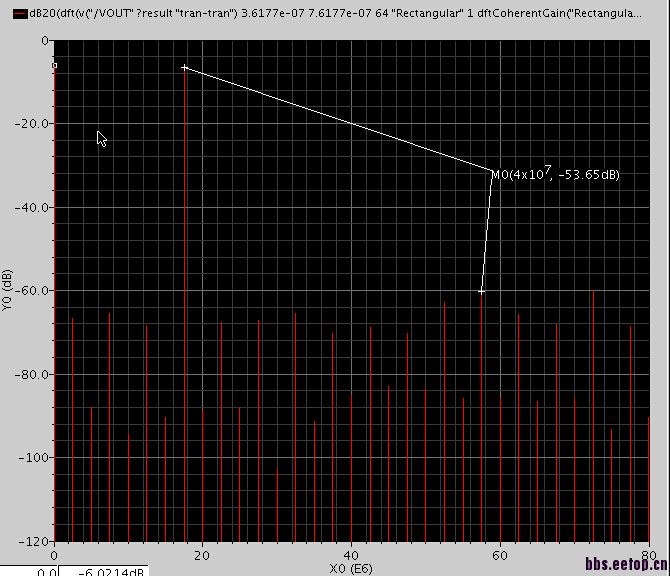

各位大侠,小弟设计了一个12b 160M采样,1.2V供电的单通道pipeline ADC,全差分 SHA/1.5+1.5/1.5+1.5/1.5+2.5/2.5+3结构,前后级运放共享。自己没设计基准电路,VREFP/VREFN/VCOM都是外接的。各级也都做过功能仿真。sHA带负载时仿sfdr有88dB。整个ADC 加入正弦波功能仿真正常,但是信噪比很低,sfdr也才53dB不知道是哪里出了问题?下图是test_bench,ADC后面加了一个12b ideal dac将输出转换成模拟量。取64个点

下图是输出结果,基本上功能没问题

下面是各级加斜坡信号仿真结果

下面是各级加斜坡信号仿真结果SHA/1(SHA+1.5)功能仿真

2/3(1.5+1.5)功能仿真

4/5(1.5+1.5)功能仿真

6/7(2.5+2.5)功能仿真

ramp input时候开头向下那几个这么突兀,是怎么回事?

底层每个stage要保证function正确,不要一下来个top的仿真,步子太大不好

你这个top的仿真,noise floor这么高,不是performance issue,是function不对

还需要debug,其实adc top输入ramp,看看是不是单调,也许会发现些什么

跑个斜坡一个台阶两个周期,就知道哪一级出问题了,你这信噪比太低,后面的MDAC或者比较器明显有问题啊~

我觉得开头那几个向下急突兀是因为是瞬态仿真,电路首先需要一个稳定过程,到后面电路稳定之后功能就正常了, 下图是我将STG6和STG7单独做ramp输入的仿真结果。2.5b/stg输出斜率是4左右没问题。

我再试试您说的top ADC输入ramp试试。还有我之前仿过100M采样下得sfdr是78dB,sndr是66dB。

您好,我不太理解您说的一个台阶两个周期是什么意思?您能稍微详细说说嘛?

这种情况最好是同样的时钟和输入加到理想ADC上,和实际比较着看

ramp输入,mdac 的residual怎么幅度大小不一?是不是ramp 太快了?但是最多也就差一个clk cycle ramp的输入的差,不过要x4

ramp输入,mdac 的residual怎么幅度大小不一?是不是ramp 太快了?但是最多也就差一个clk cycle ramp的输入的差,不过要x4

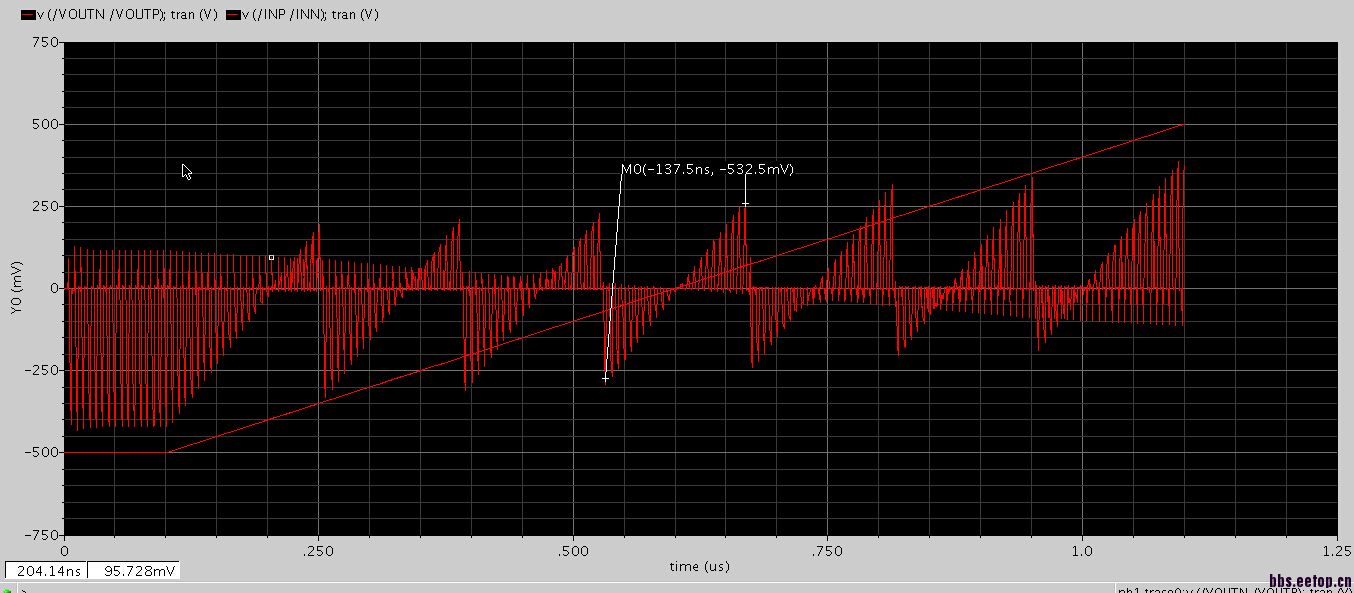

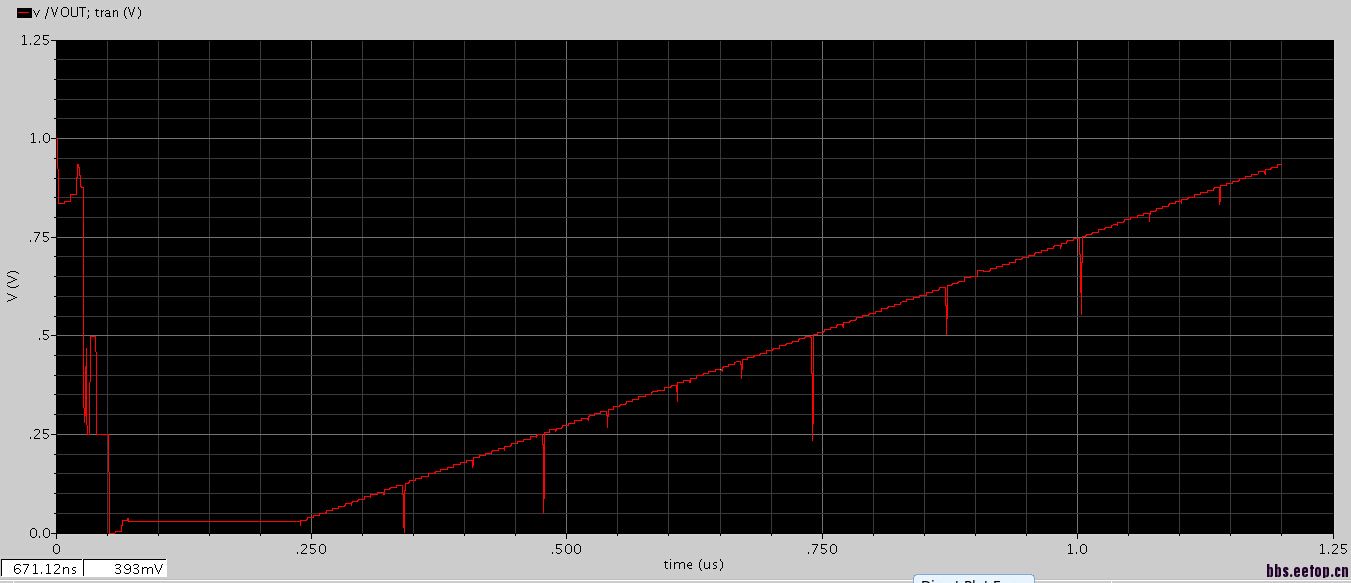

MDAC residual幅度不一我觉得可能有两个方面吧:1、比较器本身失调存在 2、电路运算有延时。不过有数字校正电路在的话,这个应该问题不大。 top ADC输入ramp的截图如下,输出效果确实很差!我再查查看!

里面不仅有许多明显的毛刺,而且怎么台阶高度也不一样啊!

窄的毛刺不要紧,是输出12bit data之间有skew,用ideal dac转换时候就会见到毛刺

在0.9us时候有个非单调看见没有

你说的没错,毛刺是高位处数据变化的时序上有skew。你说的非单调是这个?(白圈里面)

对,只要有非单调,肯定是function错,其他地方的step有大有小也应该是这个原因,不过表现的不明显

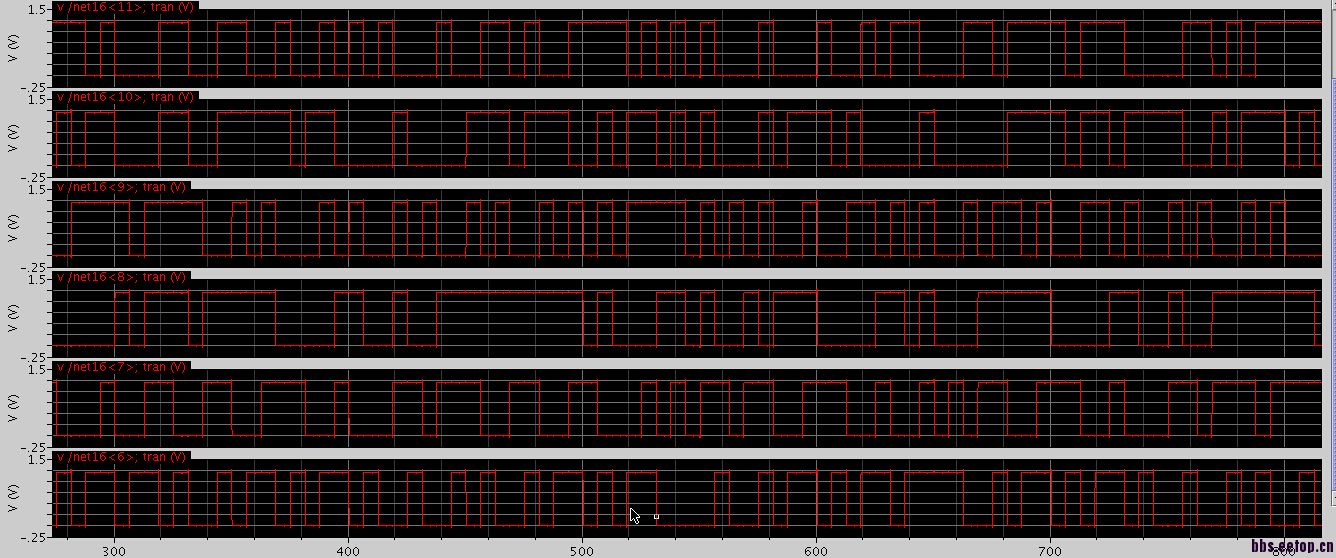

恩,我仔细再查查,之前看别人帖子她说你看到你回复就很激动,我怎么发现我现在也有点激动!对了,仿出来的步阶应该是一样高的对吧?下图是加入ramp输入之后的data output,按理来说每一位的高电平宽度应该是一样的,最多差一个周期也就是1/160M=6.25 ns左右,可是我这个在高位时还好,在6—11位(这里顺序反了)时,高电平宽度明显有问题,这里往后是两个2.5bit/stg+3b flash,所以我猜我的2.5bit级设计的有问题,我现在将这些2.5bit级全换成1.5bit级试试加ramp,看输出结果怎么样。

fuyibin前辈是eetop少有的几个在论坛活跃了8年,至今依然保持很高活跃度的坛友。他解答的问题,通常一针见血。

恩,得向他好好学习呀。

我把所有2.5bit级都换成了1.5bit级仿ramp似乎还是存在非单调。

都是前级采用高位的MDAC,后级采用1.5bit的,你这个比较独特

我是从第一级单独仿真,看其位数,然后再第一级加第二级一起仿真,最后整体

我当初这么做是觉得用多位的话,反馈系数太小,运放带宽太大,运放不是很好做,要同时兼顾增益和功耗的话我觉得高速点儿的ad,高位用多位代价太大。对了你的第一级怎么仿?后面的电路都用verilogA写?

对,用verilogA写的,只有需要测试的一级产生误差,VerilogA写的模块只有量化误差。

这样比较好debug,不然你全部搭建完,仿真,谁知道哪里的问题,不够直观吧

按我的经验吧,12bit的SFDR仿真应该在75dB以上,以前做过高度高精度的pipelinedADC

你是用VerilogA把所有的子模块(如,开关,运放,数字校正等等)写出来然后再搭一个整体,还是把所有后级的adc功能用VerilogA写出来?能把代码让我参考一下嘛?

恩。知道啦,谢谢

你说的12bit至少仿真到74dB的是 sfdr 还是 sndr ?

SFDR

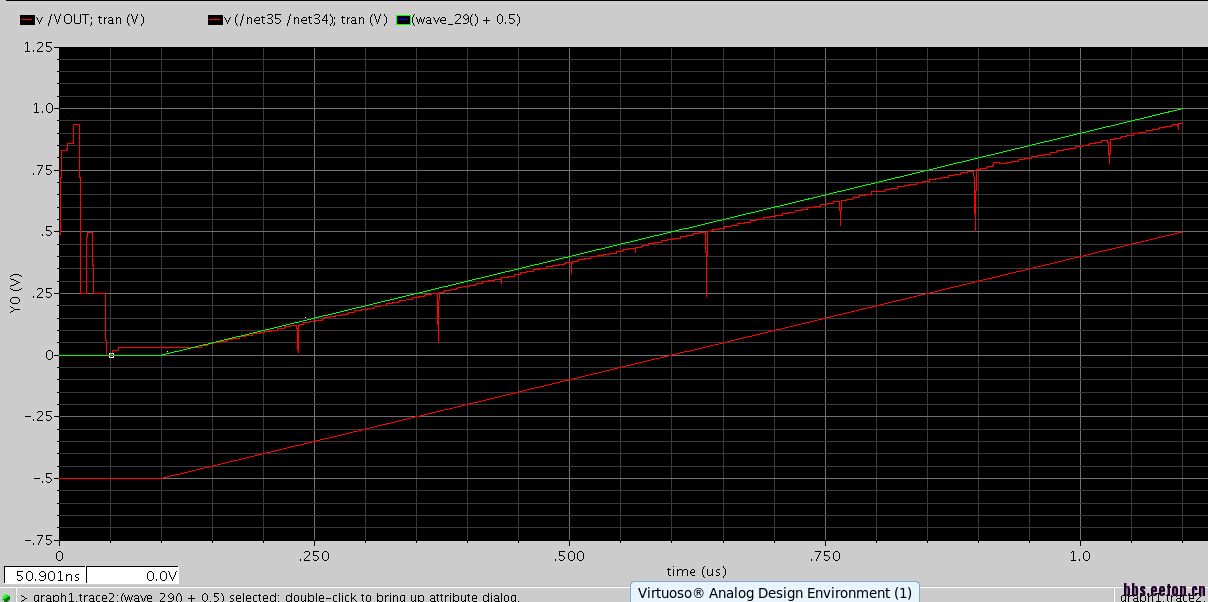

为什么呢?我问过许多人有说 sndr 的,有说看主要关注哪个的,也有说sfdr的。我觉得应该是sndr吧,作为仿真的话,没有考虑到热噪声和失配,唯一的非理想因素应该是建立误差和时序方面造成的其他误差,如果设计合理的话理论上sndr至少74dB吧?下图是我把2.5bit级换成1.5bit级的ramp仿真图,昨天忘了贴出来。明显还是有非线性。

SNDR 对应有效位数,考虑了noise 的影响,一般是比SFDR低10dB左右,比如如果你设计比较好的话,SFDR可以达到80dB,那么你的SNDR一般就只有70dB左右,对于看哪个指标都重要,它们反映的方面不同而已

仿真中可以加噪声和失配的,只要你的pdk包换这个noise model和mismatch model 信息。