dummy管子到底该怎么接好

时间:10-02

整理:3721RD

点击:

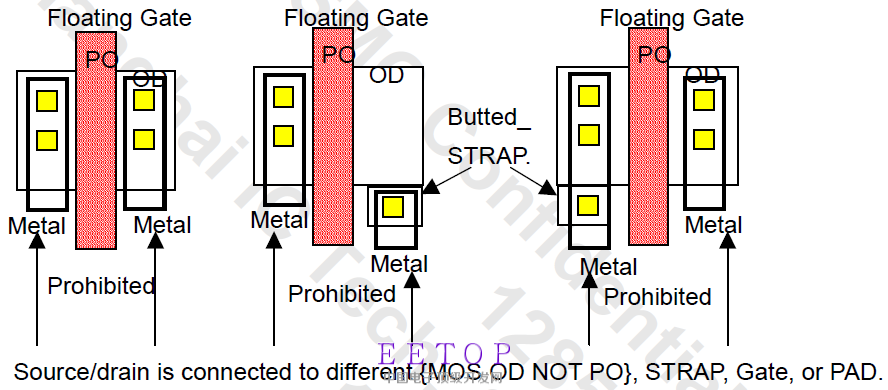

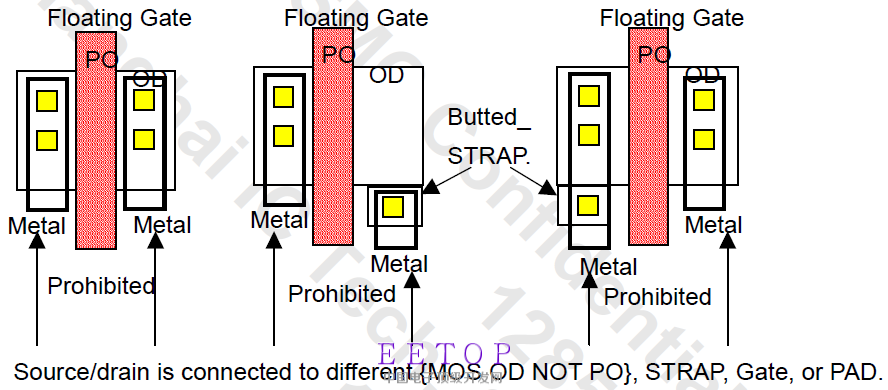

如题,小弟处在版图阶段。但是关于版图中的dummy的MOS管的接法一直存有疑问。论坛很多帖子都是说把三个端口GSD都接到一个点位上,sub接电源或是地。但是最近在看工艺厂提供的layout design rule里有提到,可以把匹配的管子的gate和S或是D做成floating,只要S和D的点位不同,如下图。

但是自己不太确定这样做可不可以,或是有没有什么潜在的问题,所以想求教论坛里的各位大牛,谢谢!

但是自己不太确定这样做可不可以,或是有没有什么潜在的问题,所以想求教论坛里的各位大牛,谢谢!

floating node的話,

Calibre ERC Rule不會pass喔!

然而好像按照design rule文件说的那样,使得SD两端同电位,或是只接S或D一端,是可以过DRC的呢,我现在只是不知道这样做会不会有什么风险,感觉可能有问题,然而TSMC官方文档里又说这样可以。

同有此疑惑。

栅极浮空会不会导致电荷积累无法泄放?瞎猜的,还请高手指点

我也见过floating这种接法的,但是个人也总觉得有可能会出现像楼上说的那种电荷积累之类的问题,所以一直不敢这么接

所以我都是把dummy的栅和不跟其他管子共用的那个有源区(S或D)接GND

还请高手们指教

看看,悬浮应该没事

想知道这样会不会有什么隐患什么的。其实自己好想画悬浮的,悬浮好省事。

见过NMOS和PMOS的D floating,对于PMOS来说,在制造过程中本来VDD就是接近地电流(放电),所以电荷都会通过PN结到VDD。对于NMOS来说也有反向的二极管放电了。

我觉得可能是这样的,天线效应的能量不像ESD那样大

gate可以floating击穿了对旁边的MOS也没影响,因为击穿的只是这个gate的氧化层,其它物理结构没损坏

浮空不挺好的吗?看不出什么问题,而且,不会有多余的走线。

工艺厂禁止的情况:dummy SD 接着不同电位,而且浮空的gate被静电荷击穿,导致短路。

哦哦,这样啊,谢谢楼上的大N们,我就放心的画了。

额,尝试过了后发现这样做貌似LVS过不了,特别是当版图中有大量的这种栅极浮空的mos管的时候,LVS分不清哪个是哪个。找了我好久才找到问题是这个。。