PLL中vco,CP的电源敏感曲线仿真

时间:10-02

整理:3721RD

点击:

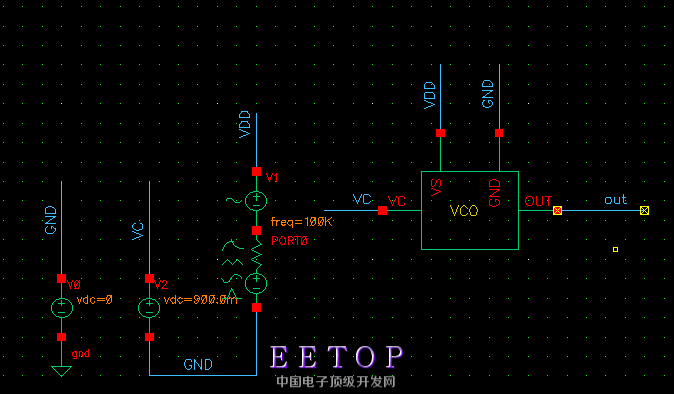

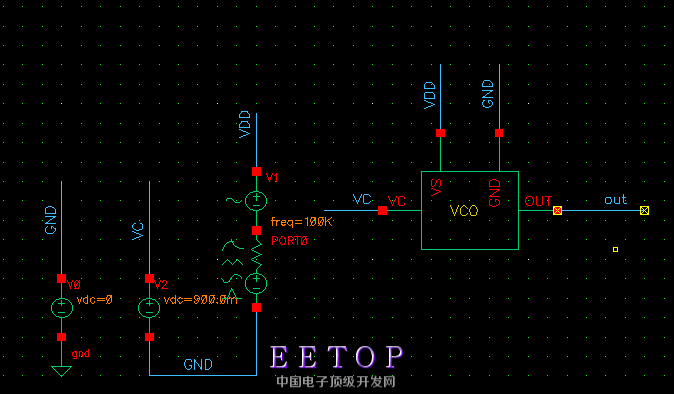

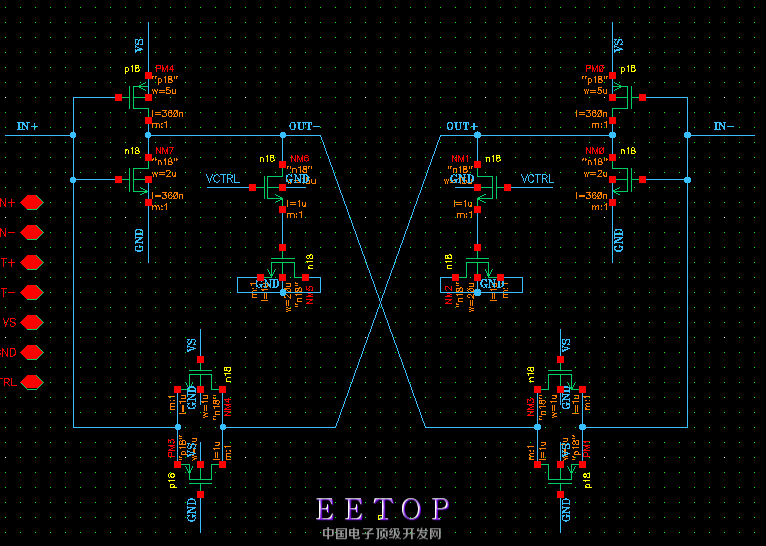

本人想仿真一下环形振荡器和电荷泵的电源噪声敏感曲线,就是VDD上的噪声在二者的输出端的影响,应该会有一顶的抑制作用。但是我只知道需要PSS+PAC联合仿真,具体设置参照自己找的资料设置了一下,出来的结果很离谱。跟论文上提供的图完全不一样。请教下做过的同学。先行李谢过啦啦啦啦啦我的仿真电路图如下:

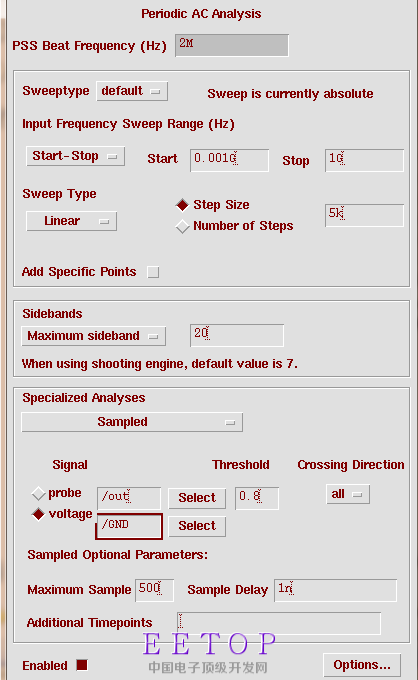

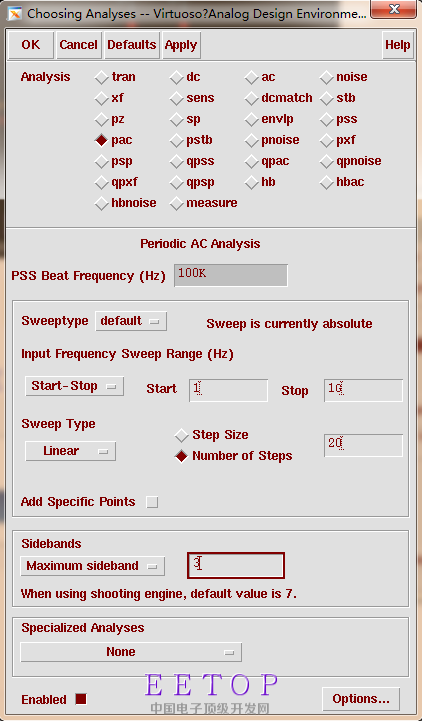

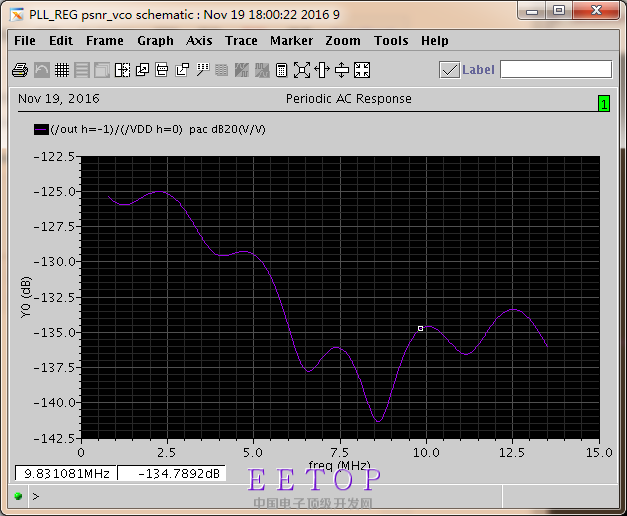

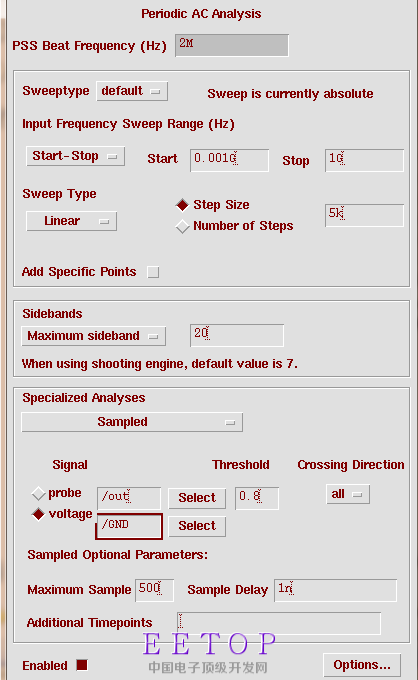

按照你给我的指导,将PAC 设置成这样,上面三张图是PAC仿真的结果,PSS和PAC 的设置。结果已经达到-120DB左右,应该是不对的。麻烦你帮我看下还有什么设置不对的地方?请直接指出。谢过

PAC仿真设置如下:

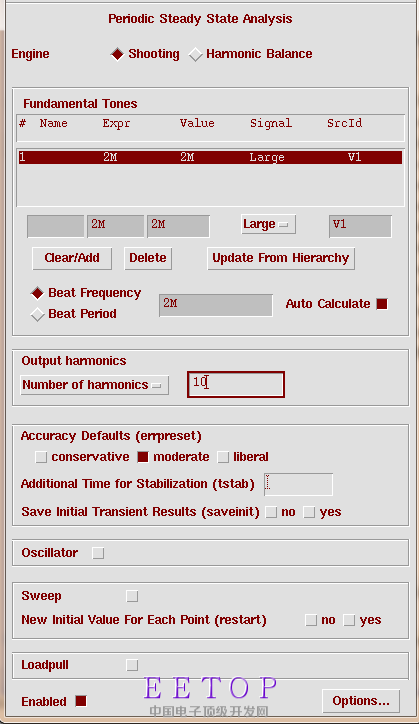

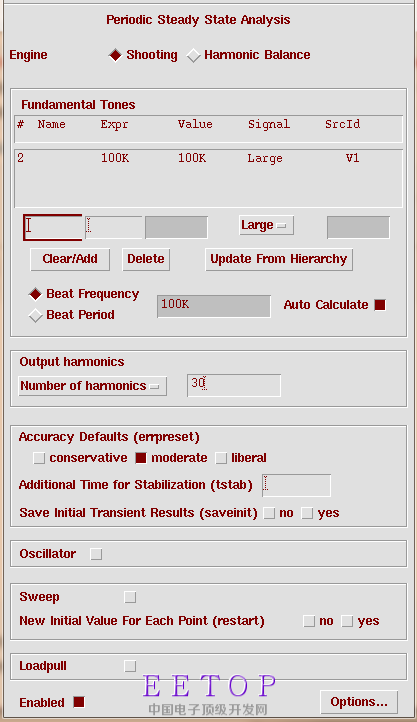

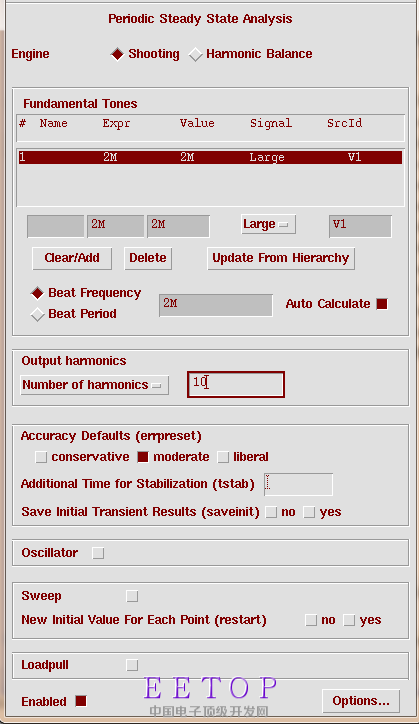

PSS设置如下:

问下做过的大虾。我这些设置都对吗?还有什么设置的地方没注意到。谢谢

建议用pxfsampled. 不过你single-end vco本来就没什么psrr,还能离谱到哪儿去?

我用的VCO 延时单元是下面的结构,三级延时单元串联,一级反向,应该不是单端的VCO。

其电源噪声抑制比应该是小于零的吧?我觉得我的仿真有问题,可能是PAC什么的设置不对

你的第一个图里面只有一个输出,有双转单?

PAC也要设置成sampled才会找到合适的点。你的结果有除edge rate吗?

按照你给我的指导,将PAC 设置成这样,上面三张图是PAC仿真的结果,PSS和PAC 的设置。结果已经达到-120DB左右,应该是不对的。麻烦你帮我看下还有什么设置不对的地方?请直接指出。谢过

还有一个问题,就是我PAC中,我设置的跑的频率范围是1M-1G,为何PAC跑到14M就停了?

以前没用过这个仿真,差的太多

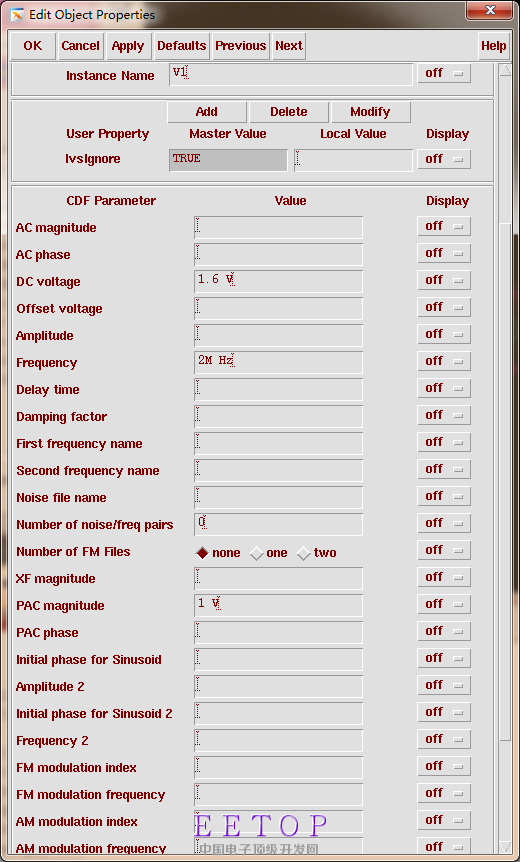

这个是我PAC设置的信号源,采用的vsin,请过目哈

你的PSS设置是错的,你应该设置成oscillator. 而且你的VDD不应该设置频率。