带隙基准 BGR 温度曲线问题

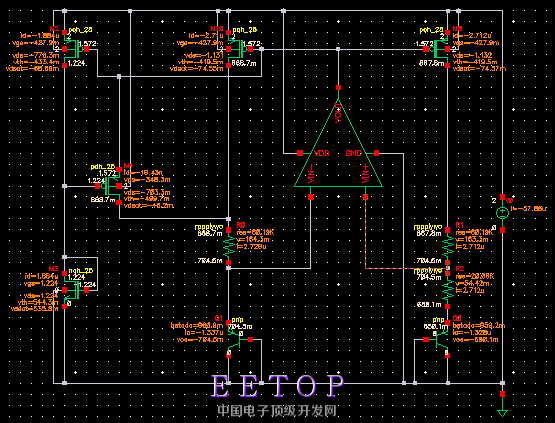

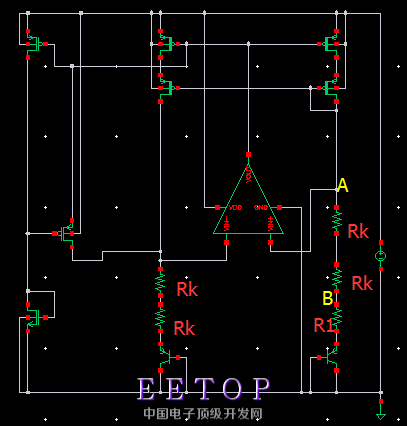

下图是电路图

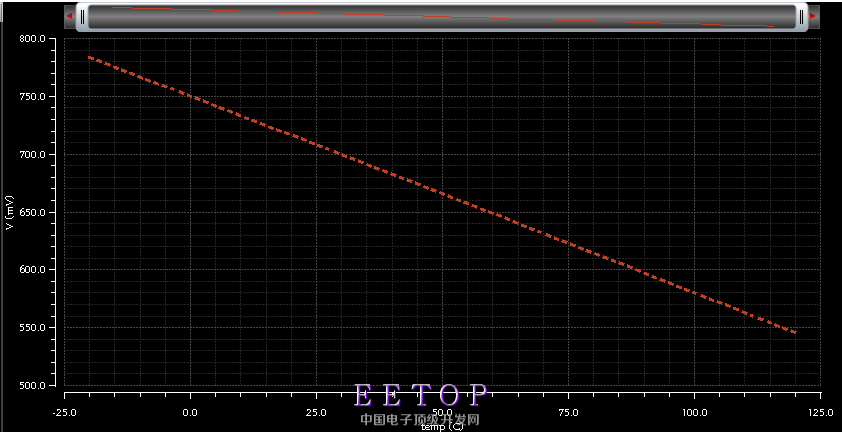

就是那种最简单的BGR拓扑,然而对输出进行温度仿真,确实这样的,都快成了CTAT了,-20度到120度变化了有200多mV

明明以前用别的工艺做还好好的。

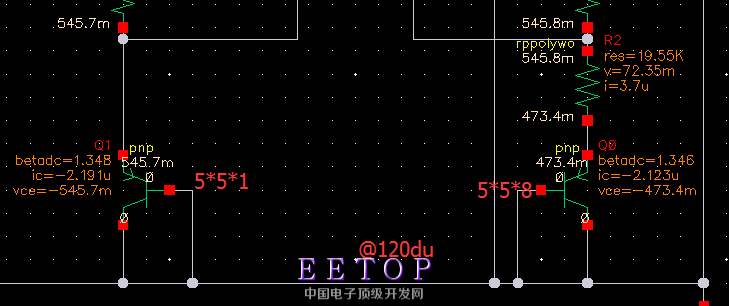

这次用的是TSMC 65nm,两个pnp管子分别用的尺寸是5*5和5*5*8,图中电阻用的是rppolywo,左右两路电流有3.7uA左右,

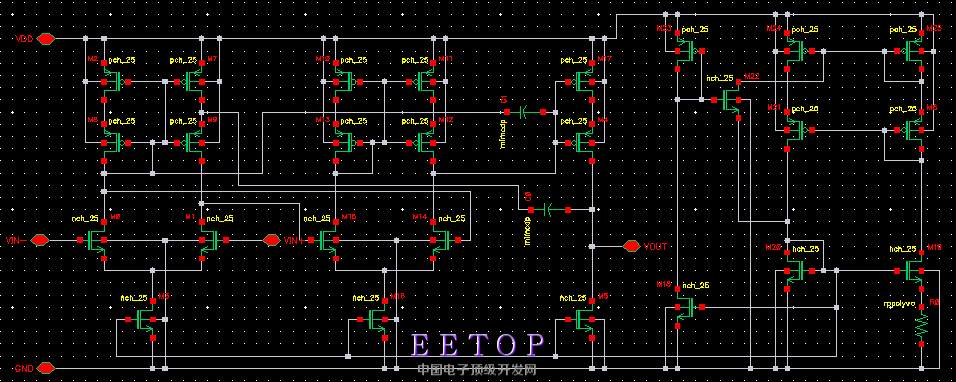

开始我以为是OP在某个温度节点不工作了什么的,然而仿真发现都还好,下图是用的OP

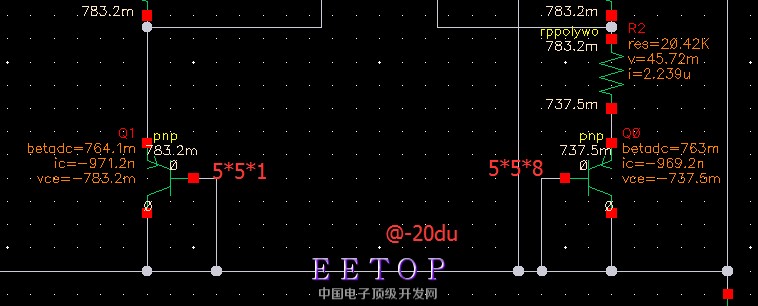

实在搞不清楚为什么,我又看了下PnP管子在-20度和120度下的ce电压,感觉有些怪,变化有些大了,如下图

变化了有200mV的样子,这样正常吗?还请高手指教,谢谢!

电阻还要优化

调一下R0 R1 R2的电阻让你的vbg达到1.2V左右

P管的匹配程度也需要注意,而且,我觉得这个规模,三极管1:6就够了

你要保证在一个温度下有0的温度系数,才能出现那种弧形的曲线,现在温度系数在整个温度范围内都是负的,所以你要增大输出那里的那个电阻值

增加R1/R2

谢谢上面各位的回复!

确实是电阻小了,我加大了两路上的RK电阻,把A点电压抬升到了1.21V然后温度曲线就正常了。

但是现在我又有点疑问, 为什么要A点的电压抬到1.25V左右才可以呢

我最开始设计的时候是想着得到一个比VBE要大的ref才在左右两边都加了等值的电阻Rk的,但是却发现本应该在B点输出的VREF的温度特性非常差,系数是负值。然而发现A点输出的温度特性要好得多。

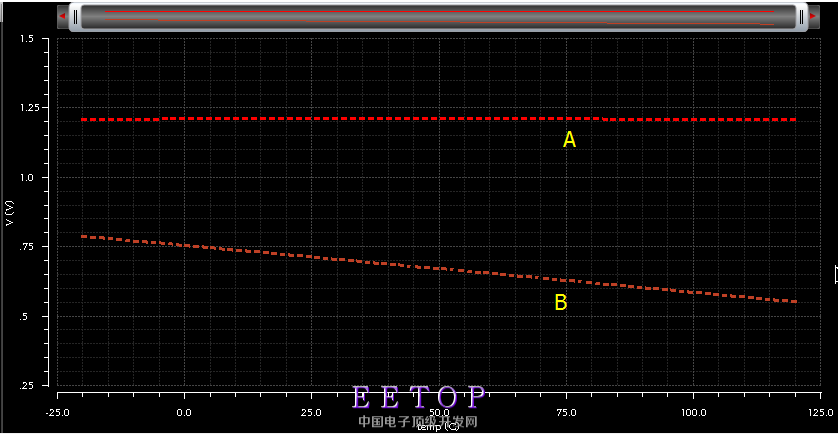

下图为A点和B点电压的温度扫描

现在有些疑惑的是,不是应该按照书上的在B点得到温度系数为零的电压吗,为什么却在A点。

我自己感觉是因为公式“Vtln(mn)”里的这个“mn”值设置小了(我的左边pnp管为1,右边pnp管为8,上方左右两路的PMOS管的尺寸都一样),所以导致△VBE的正温度系数不足以抵消VBE的负温度系数,所以需要借助上方电阻的正温度系数来是的总的温度系数变为零。

不知道自己这样思考对吗?

还请牛牛们指教!谢谢!

看起来你已经在运放的正输入端绘制了电压。 所以你在绘制Vbe。 曲率是正常的。 曲线Vref曲率将不同。

可是我还是不太清楚为什么把A点调到1.25V左右才能出来那个温度coefficient为0的电压?

书上说的1.25V不是在上图的B点得出的电压吗?为什么在这里叠了一个电阻还是1.25V呢?

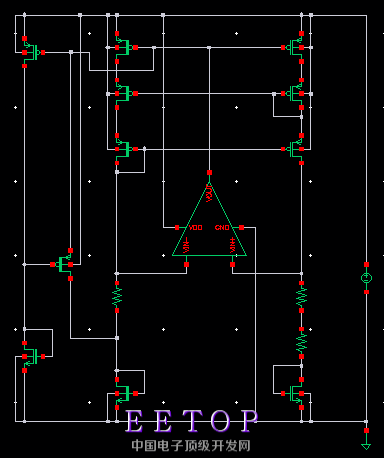

还有,为了得出基准电压小于1.25V的电压,我也尝试了别的结构,如下图的β倍增基准。

通过调节电阻的值,来使得运放的同相输入端的电压电压的温度系数为零。通过调节,也可以得到比较好的温度特性。

现在就是想问问各位高手们,和BGR相比,这个有什么明显的缺点吗,或者说和BGR相比这个的实际版图测试结果和仿真结果会差得很大吗?

自己实际做的时候,想用这个结构,输出的Vref的电平水平更符合我的应用要求,并且面积也比上面的那个BGR稍小。

看了半天,觉得小编基本原理都没有弄清楚,需要再回炉去看书

电阻比例是要根据Vbe的温度系数,和delta Vbe的温度系数以及bipolar的比例计算出来的

得到一个大概准确值,然后再进行微调得到含有里温度系数点的曲线

还有一点关于bandgap的结构认识错误,这对成比例的bipolar是用来产生delta Vbe 和PTAT电流的

谢谢大神回复指正,小弟确实是萌新一枚,正在回炉重造中。之前我也是想先大概算一下再设计的,但是最后因为不知道VBE和Vt的温度系数也就罢了,用的ADE多参数扫描的方法确定的电阻值。

想请教下不同工艺下的VBE和VT的温度系数是不是大概一样的呢,还有这种参数一般在哪里找呢。

这电路之所以叫带隙基准电路,就是因为基准值差不多等于带隙值,1.2V

bipolar跟工艺关系不太大,就像一般的pn结正向导通都在0.7V左右一样

建议去看拉扎维关于bandgap设计的那一章

您好,我也用的tsmc65做的带隙,现在到后仿了,不知道你对T65版图设计规则了解不

这个的话,你可以参考TSMC给出的layout design rule文件,里面写的很详细的,我也是看那个学习的。