pll锁定时间

时间:10-02

整理:3721RD

点击:

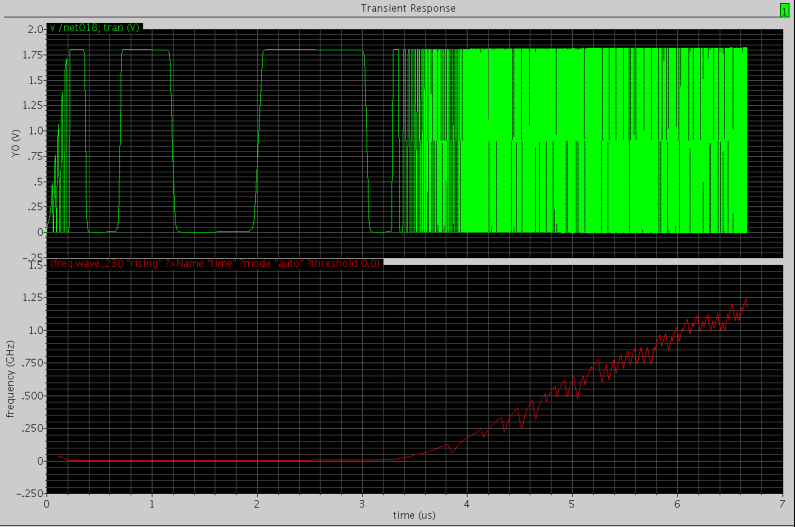

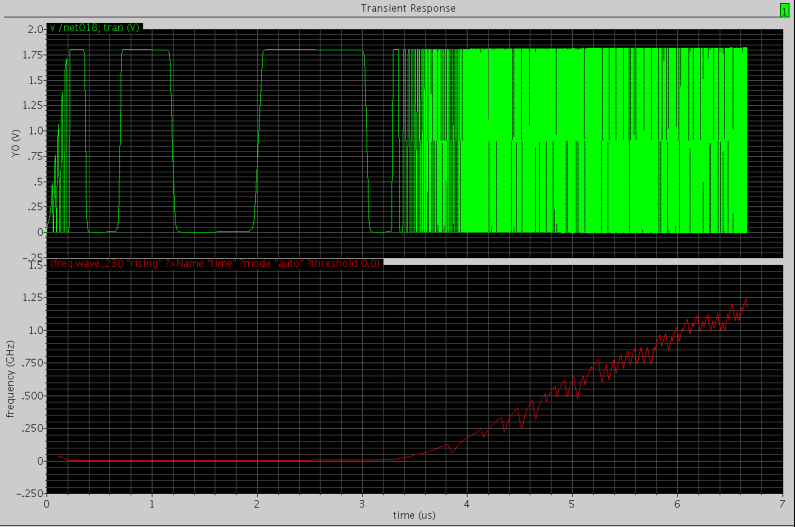

我的输入频率30M,输出1.5G,N=50,Icp=100u,Kvco=2.7G,带宽1M,最后仿出来的的锁定时间17u,别人的这么大带宽锁定才4u,而且我的频率是从上往下掉

第一个是fvco,第二个是vctrl,第三个是Icp

第一个是fvco,第二个是vctrl,第三个是Icp

给个上电的话就会有一个空档,然后再慢慢锁定,很奇怪,求助

给个上电的话就会有一个空档,然后再慢慢锁定,很奇怪,求助

第一个是fvco,第二个是vctrl,第三个是Icp

第一个是fvco,第二个是vctrl,第三个是Icp

大神们快帮个忙吧

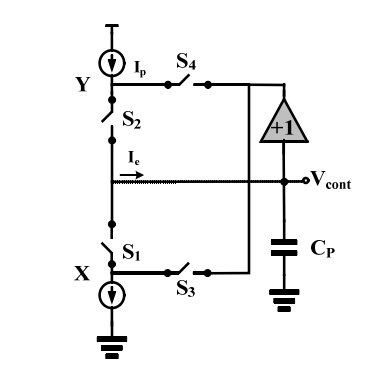

好像Icp在变化。可以在启动是把Vctrl拉到中间电平先。

初值设定在中间电平的话,能代表我真正的锁定时间吗?

而且我的初值为什么是高,vctrl我都没设置初值,

初始是dc收敛计算得到的。

pll频率牵引是大信号过程,sr不够所以很慢

怎么算,能详细说明一下嘛

还有大信号过程怎么理解?怎么看?怎么仿

不是仿真设定,我是说PLL电路里面加启动电路,启动是把Vctrl拉到中间电平。

这样啊……我把pfd换了个结构,锁定时间就快了,不明白为什么,但是电源电压

给个上电的话就会有一个空档,然后再慢慢锁定,很奇怪,求助

给个上电的话就会有一个空档,然后再慢慢锁定,很奇怪,求助

你原来的PFD是不是只是PD?

不是,

比带宽大,最好是比PFD时钟频率大2-4倍。

你都选在什么样结构的pfd呀?

控制电压最后从高定平还是低电平开始,是和PFD的输出控制CP的开关有关系

发生了csp,可以试试把充放电电流变大,锁定时间会减少

你说的仿真那个曲线貌似不是真正的锁定时间

请问锁定时间怎么看啊?我是看vco控制电压在10mV左右 但是没有根据 请问您是怎么看的?

看一下