二阶sigma delta ADC modulator低频噪声大的问题

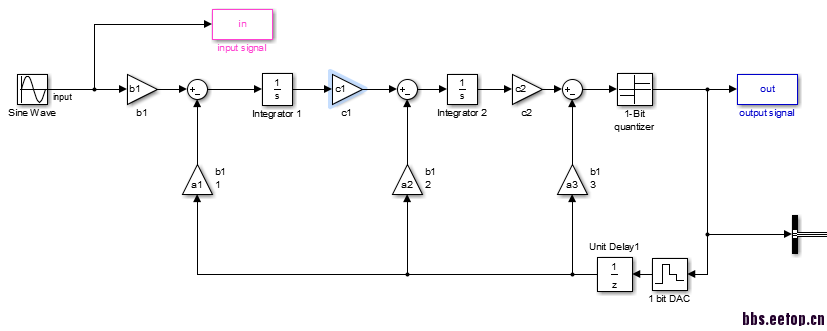

在做一个二阶2bit的sigma delta ADC, CIFB结构,matlab建模的snr可以达到85dB左右,在cadence里面用理想放大器构成的积分器,理想的DAC,还有ladder flash ADC,bandwidth=200KHz,osr=80,fs=32MHz,fin=101*fs/2^14,coherent sampling,但是cadence里面最后moudulator的输出导入matlab计算snr。

1 如图,第一张图和第二张图,可以明显的看到在接近dc的那几个bin的noise明显很大,导致最后算出的snr很小,去掉那几个bin可以得到snr达到70多dB。我想问的是有什么原因导致的低频下的噪声很大呢?我之前看过一些帖子,也没整明白,说的是有可能是积分器里面的gain bandwidth和slew rate的问题还有dac反馈的问题,我都试了,还是没能解决掉。

2 图3,从fft分析的频谱来看,明显的存在着频谱泄露的情况,这又是什么原因呢?(采样点事严格按照coherent samping来选取的),有哪些因素可以导致频谱泄露呢?放大器的非线性?我的放大器是verilog——a代码写的,怎么来改善它的线性度呢?

最后一个图是和matlab建模输出的fft的比较。

困扰了好久,谢谢大家,踊跃讨论!

顶一下 等大神

低频不用算SNR,那是offset不用管它。

低频的是直流offset,可以不管它。看你电路仿真的频谱,噪声明显偏大。你可以把除了你怀疑的以外全部换成理想模型再试试,排查一下

谢谢回复 搞定了 把那个直流分量去掉了 是应该吧modulator的输出从0 1换成-1 1就行了

现在已经把dc 去掉了,snr也还可以,因为我这个采样里面fin差不多等于bandwidth,带外的噪声大就不影响了,但是我发现频谱中存在奇数次谐波,这个应该怎么排查呢?我这是连续时间adc 积分器用理想的dac理想的,非线性是不是在quantizer里面引入的呢? 谢谢回复

把仿真步长设短一点

gain bandwidth和slew rate对谐波的影响较大

这个对什么有影响呢?

我的积分器 是verilog写的放大器 里面没有slew rate这个参数 bandwidth 改变了影响不是很大 谢谢回复

modulator如果用01,积分器很容易饱和,这一点在高阶SDM中特别明显。如果用simulink来做一定要用sign模块来代替1-bit量化器

小编你好,我按照的 Understanding DS DATA converter里面320页的结构搭的

二阶1bit的sigma delta ADC, CIFB结构,simulink里建模

我的疑问是对于DAC 是用zero order hold模块 ?

是的,我是用的这个

我卡了很久 介意发我看看你的 simulink的模型么 我的邮件时geonj24@gmail.com如果不行 能发个截图给我看看么 ?

谢谢啊

好的 等我抽空截个图

特别感谢! 不急等你空就好 谢谢!

小编也给我发个simulink的模型截图 我的邮件时1045181788@qq.com谢谢

小编,请问从cadence中导出了modulator仿真数据,在matlab中进行fft变换时的matlab程序该怎么写呀?是不是与一般的数据做fft变换不同,要考虑到OSR的问题,要把过采样频率转换为奈奎斯特频率呢?具体应该怎么呢?多谢