无输入参考时钟情况下,pll是否有频率信号输出

从仿真结果上看没有,但是芯片测试却有频率输出,感觉整个环路会使得PFD不断地降低CP输出的电压,最终应该稳定在VCO不再振荡才对。

请指点。

VCO肯定会振荡的,因为本身噪声就会放大,使得VCO振荡。所以有输出是正常的。

我的想法,仅供参考!

如果有频率输出,那么PFD就会比较两者的相位,感觉最终会使得VCO的控制电压或电流减小到不再振荡,这时已经没有增益,有噪声也没有用吧。

上面问题的提出,是因为部分芯片在无参考时钟输入的情况下,无输出,当提供参考时钟后也无输出,而无参考时钟输入的情况下有输出的芯片则可以锁定。

所以希望明确2个问题:

1、无参考时钟输入的情况下,有频率输出的原因(仿真没有仿出来)

2、无参考时钟输入的情况下,无输出,当提供参考时钟后也无输出的原因

谢谢。

PFD会保持高电平或低电平,从而使得CP输出饱和,稳定在电源电压或gnd,因此VCO就会有输出。无参考时钟输入下,无输出,应该是VCO没有震荡,导致加了参考时钟后也没有输出。设计时最好加一个启动电路

1、PFD为什么会保持高电平或低电平?不是应该输出参考时钟和反馈时钟的相位差吗,请再解释一下。

2、VCO没有振荡,是因为vco控制电压到达电源电压后的vco增益不满足起振条件吗,说明设计临界使得部分芯片不起振?

PFD部分可以看下其实现原理,当只有一个输入时,自然是一路为高电平,另一路为低电平而振荡器不振荡原因很多,受PVT影响

不管电荷泵输出电压为多大(0~VDD),VCO应该都能振荡,只是振荡的频率不同。也就是说,CP输出的电压只是起到调节VCO输出频率高低的作用,而不是决定其能否振荡。

至于“有参考频率也无输出”,那应该就是VCO没有起振了。

不起振的VCO,看可否增加偏置电流么,也许就能够起振,或者更改环境温度试一试

环路本身会让控制电压趋于0,但主要还得看2点:

1,VCO 在 控制电压为 0 时 是否还在振?

2,输出级在VCO不振的情况下是否有频率出来?

看一下无输入参考时的输出频率是多少不就知道到底是什么信号了吗

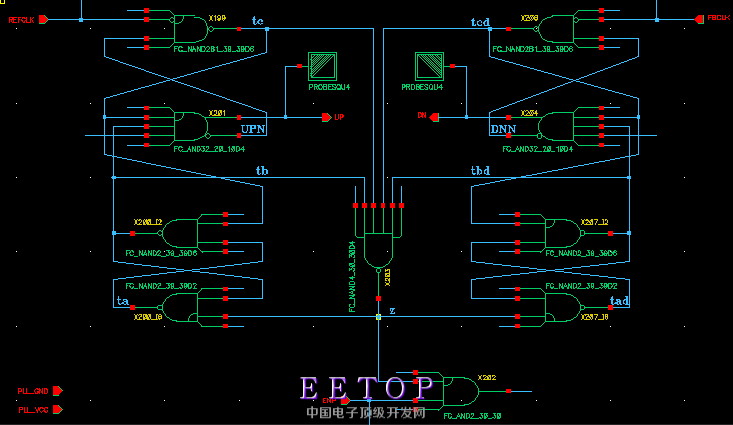

图片是PFD的电路图,如果复位正常,UP和DN均为0,代表后面CP模块的上下current source/sink均关闭,那么CP输出即VCO控制电压就不会爬升到电源电压,VCO也就不会振荡。现在怀疑是复位不正常,使得UP为1,DN为0,这样VCO控制电压充到电源电压使得VCO起振,FBCLK虽然有VCO输出的分频信号进来,但是改变不了UP和DN的状态。

所以我的理解是在无参考输入时,如果内部没有特别设计让VCO可以free run,比如我这个电路,VCO是不会振荡的,直到参考输入进来才会频率由低到高逐渐跟随锁定。

1、仿真中,当VCO控制电压为0时,VCO的确有振荡,但是频率值很小,VCO中差分放大器的尾电流就只有几nA,这种结果不可信吧。

2、“无参考时钟输入的情况下,无输出,当提供参考时钟后也无输出”,我同意大家说的VCO没有起振,而且倾向于VCO电压到达电源电压这个数值时VCO没有满足起振的条件,但是我后仿各种PVT并没有发现不起振的情况,请问4级全差分放大器的单级增益指标要做到多少才能起振?大于square root(2)吗?

VCO没有输入也是会振荡的啊,你用的什么机理来调频的?

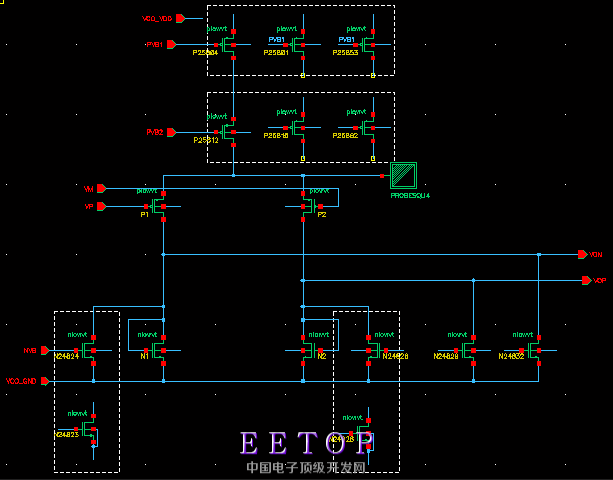

4级全差分放大器组成的ring osc,放大器的tail current=镜像系数*IREF,IREF=vco控制电压/电阻

无参考时钟,有没有做gating,是拉到固定 的0还是可能被couple一个 clockPLL输出是 精准的 还是 在变化,看一下 phase noise是锁定的还是 free runing

我大概知道你电路结构了,你应该把尾电流源电路贴出来,这样才能理解你说的为什么控制电压是0的时候会有振荡输出。回到问题,你没有输出的片子应该是本身电路设计存在缺陷,无法起振,不论你输入是有还是没有。具体原因就就需要实际分析了,起振条件很好满足,应该是其他原因,比如某个电容击穿了。能说下你现在没有输出的片子大致的比例么?

设计目标:参考输入时钟24MHz,输出480MHz;

测试方法:480MHz信号经过计数器40分频后,连接到数字IO,测试时确认该IO管脚有12MHz的输出时钟信号,后面说的pll无输出都是指该IO无输出

测试结果:有部分芯片多次上下电会有概率性的pll无输出

这几天的测试结果:

1、之前说的的参考时钟输入有点简化,实际上是芯片内部的xtal电路的输出作为pll的参考输入,而xtal模块的xin和xout外接24MHz无源晶振(典型应用)

之前提到无输入参考时钟,是指将xin与无源晶振的管脚断开,这时发现pll有比较稳定的频率输出,但后来发现这种连接方式很容易让xin耦合到板子的噪声,

经过放大后还是会传到pll的参考输入端;所以直接将xin接地就没有这种稳定的频率输出了,现在的pll输出表现形式是大约70%的芯片仍然有状态翻转,但是不是固定频率,很随机,另外30%的芯片表现为状态固定。

问题:

基于我之前的VCO电路描述,这种输出正常吗?这种条件下的仿真结果是有固定KHz的频率输出,但是VCO的工作电流只有nA级,我不确定仿真的真实性。

2、测试pll的锁定范围,确认范围是1~40MHz,当输入参考时钟的频率超过40MHz后会失锁,用探针扎在预留的vco控制电压的probe pad上,发现电压基本接近模块的电源电压,虽然探针引入200p左右的电容,但感觉结果还是可信的;

上面提到的失锁,芯片有2种表现形式:一种是失锁后仍然有频率输出,减低输入参考时钟的频率到40MHz以下时,芯片会继续锁定;另一种则是失锁后无频率输出,即使参考时钟回到锁定范围内,仍然无输出,这时模块的电源电流接近16MHz输入时的数值,初步判断vco停振,vco控制电压爬到电源电压;

问题:

当超过锁定范围后vco会停振,这可能是什么原因?

3、去掉无源晶振,改用外接时钟到xin管脚,在芯片没有上电时就先输入时钟,发现这种方法可以最全面的筛选出失效芯片,具体表现是失效芯片无时钟输出,好芯片则锁定。

问题:

下面的分析是否合理:上述测试方法则是感觉有点类似让vco从高向低这种方式启动,那些在vco控制电压为电源电压时不能起振的芯片会被筛选出来;

而之前问的"无参考时钟输入的情况下无输出,当提供参考时钟后也无输出的原因",应该是某种原因在上电期间使得vco控制电压爬升到了电源电压,已经不起振,再输入时钟也是要将vco控制电压往大了调,更不可能起振。

第一个问题,仿真有kHz的输出,此时尾电流管应该工作在亚阈值区,符合nA级的电流,反向级gm下降,但还满足震荡条件时,是有可能振荡的;第二和第三应该算同一个问题,就是说部分芯片在失锁后失效,我想问下当失效后,下次重新上电,输入在锁定范围内,该芯片还能重新锁定不?还是说该芯片就废掉了?

谢谢及时回复。

第3个问题筛选出来失效的芯片,如果重新上电后,再输入时钟,芯片还是可以锁定的,芯片没有坏掉,感觉不是电气上的损坏。

停振的原因有可能是尾电流管栅极电压太高,从而MOS管上漏端电压变得很大(Vs-Vth),加上此时反向器NMOS的体效应,阈值电压升高,有可能使得反向器输入电源电压也无法导通NMOS的情况

这是one stage的电路图,我在各个corner仿真确认ac gain,tran也确认vco控制电压如果从电源电压开始,会起振并最终回到合理位置。

原因可能还是每一级输出电压太高导致后一级PMOS无法导通,但这个无法解释当控制电压下降后还是不能起振。工艺角仿真并不能代表实际的电路运行情况,你试着用monte carlo仿真下,看能不能把这种失效仿真出来