求助关于LDO输出不对的问题。

下载 (46.17 KB)

下载 (46.17 KB)1 小时前

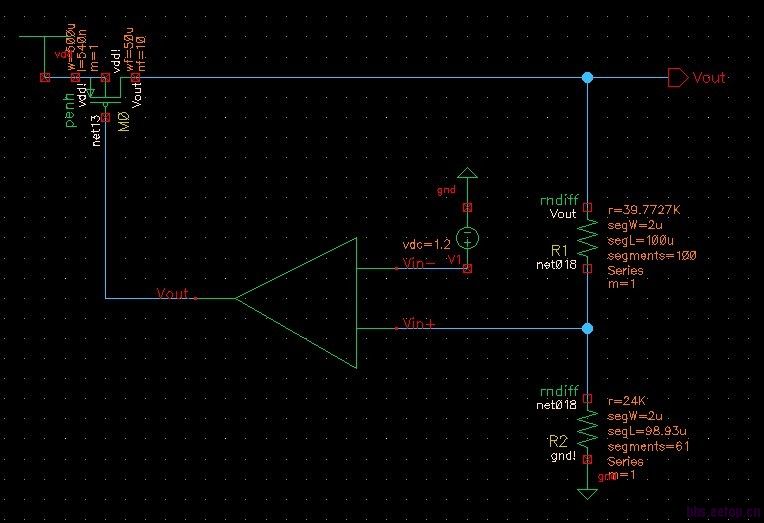

。(1)其中基准源已经确保1.2V,(2)反馈电路在5V的输出时候,反馈点电压是1.7822V,基本满足反馈的要求。(3)运放的环路增益有60db,相位裕度有50°。(4)功率管的尺寸是500/1。

我期望的是LDO稳定输出3.3V,在5V供电下。

但是实际测试的时候LDO的输出数据如下:

1)VDD=5v LDO=3.85V

2) VDD=4.5V LDO=3.70v

3) VDD=4v LDO=3.52V

一个是LDO输出不对,另外个LDO的输出和输入关系太大。这是什么原因呢。求教啊~

提供的信息太少了..基准是1.2V,反馈节点不是也应该是1.2V么?你确定运放正常工作了?我咋觉得运放有管子工作在线性区了

负载电流多大?可能已经进入线性区

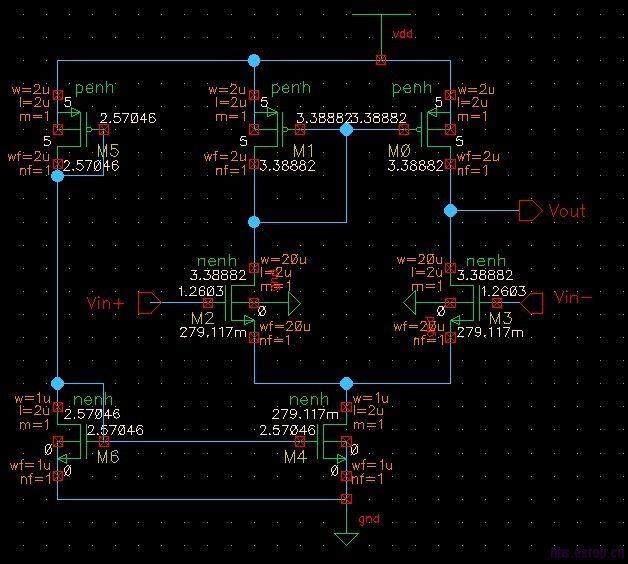

因为LDO只拉出了个输出,其他点一下看不到,需要去FIB那看。我感觉反馈比例是对的,那输出不对的话,反馈节点不会是1.2V了。运放不知道正不正常工作,但仿真时候环路增益是60db,直流点是正常的。运放结构如图

同做ldo的提醒你一下,第一你的第一级恒流源以进深度线性区,第二请问你上图的VOUT工作点是不是在没接负载时的?如果是没接负载的值,你的Von约等于1V左右.如果你这是空载时的值,那么你一加负载你觉的你VOUT的电压会怎么变?还有你的补偿电容和输出CL电容加没加?

恩,非常感谢哈。(1)看了下第一级是进入了深度线性区,而且电流镜像没镜像过来,只有4uA并且不稳定,对于这里会怎么影响呢?(2)Vout是在没接负载测的,我不清楚Von 1V左右有什么影响。试了下加电阻负载后,运放的输出电压大幅下降,但是在LDO里面我的运放直接和PMOS功率管相连,只有负载电容,那样的话运放输出貌似没什么影响。 (3)补偿电容没加,影响了频率特性。但(1)(2)里面的两点我不知道怎么影响电路了。

想问下负载电流 指的是什么~

负载电流是指,输出端到gnd接了电阻以后的输出电流,如果没有接电阻,就是空载

电路有两个问题,一是OTA的直流工作点要正确,二是驱动管是pmos,要补偿,保证在负载0~Imax范围都稳定。

我觉得主要在运放上面,上面的镜像电流源尺寸太小,Vout最大输出电压太低,导致输出管工作在饱和区,因此输出电压对电源波动,这个是一级运放无需补偿,完全稳定。

(1)运放输出接了电阻(500K)到GND后,运放的输出变的很小,只有 0.9V差不多,输出电流由几uA。这说明什么问题呢?(2)直流工作点中镜像电流源工作状态是不正确,他影响了增益,但为什么仿真时还能通过,很好的工作,并且增益还比较大。

(1)Vout最大输出电压太低指的是输出摆幅太小吗?(2)输出管不是要工作在饱和区的吗?

驱动管的宽长比怎么设置呢?

你好!想请教一下,我目前在做一个LDO输入电压1.8-3.3,输出电压1.2,负载电流电流80mA。我按照1.8V的电压电源设计,目前出现的问题输入电压在1.5——2.0V时输出电压能稳定在1.2V,当输入电压>2.1V时,输出电压将明显明显不能稳定在1.2V。通过仿真环路,在电源电压1.8V时,GAIN 80+dB,PHASE 80,但是当电源电压升高到3V时,GAIN 下降的很厉害只有几dB。调整管采用PMOS,误差放大器采用PMOS输入对折叠共源共栅运放结构,能给点意见吗?谢谢!

你肯定有管子不在正确的工作区间了。

你这个LDO结构怎么这么简单?

你OTA偏置电路就用两个电阻?电源抑制太差了吧

这就流片了,流片不用花钱?