LDO限流保护电路会振荡

不知道限流保护与误差放大器环路之间的稳定性该如何考虑与设计

限流环路稳定性问题

限流环路稳定性该如何考虑呢?

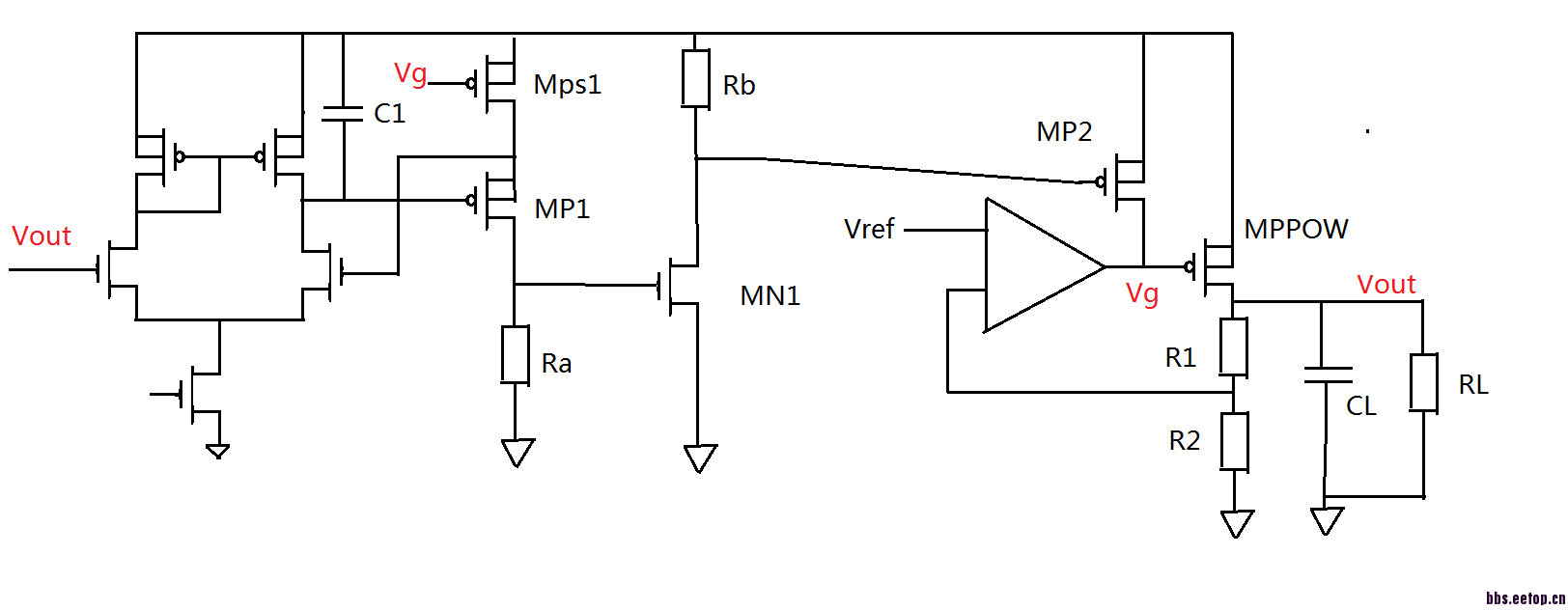

限流保护电路如图所示,右边部分为误差放大器以及输出管,MPS1是电流采样管。

限流状态的环路稳定性应该从哪个点断开?

毫无头绪。

即便告诉你可以从某个确切点断开来进行仿真,仿出来结果不行,你又能怎样修改?

复杂环路我的经验是还是需要从瞬态仿真结果出发。误差放大器自身有个带宽和驱动,MP2驱动肯定相对要强,这样我觉得限流保护环路的速度应该要慢下来,即C1处设定为主极点。如果先不考虑保护环路的响应速度,不妨将C1加大几个数量级看看

抱歉这个方向我也没做过。说出来也仅供参考,别拍砖头。

如果限流保护需要很快,那就要用另外一种设定:MP2的驱动会非常快,则需要将其驱动力限制在误差放大器驱动力以内,即MP2全开的时候,误差放大环路也能动,但是输出范围受限。

说明 低电流负载 不稳定

我估计你的电路 在空载情况下也不稳定吧?

你按一下步骤做:

1.保证在限流发生前,LDO的主环路是稳定的。如200mA的LDO,在400mA过流,那你要保证350mA时候LDO主环路也是稳定的。在频域和时域验证。

2.若1得到保证。检查限流环路,限流环路也有2个环路:一个是放大器钳位的环路,一个是限流主环路。

这两个环路都要在频域保证稳定性,足够的相位裕度。而限流环路稳定性仿真在过流时候去仿真。如400mA负载下。

3.若你不了解限流的两个环路,我告诉你:放大器钳位的环路在钳位放大器输出加probe,仿真stb。限流主环路在MP2的gate加probe,仿真stb。

最好频域相位裕度保证后,在trans 在各个corner下验证过流过程。

请问你在哪个公司工作?

空载条件是稳定的,限流保护是在进入重载后,发生的,应该跟空载条件没什么关系吧

我这个是300mA LDO,限流保护做在450mA,一进入限流点就发生了振荡。也有版本RA做的比较小,限流做在600mA,进入限流点直到输出电压下拉了很多也没有振荡。

如果缓慢加输出电流的话,在进入限流点之前,输出电压都是稳定工作的。

你说的1 可以排除。

2的话:加载MP2栅极的话,仿真时候相位裕度确实不够,大概是-9~-20;根据之前450mA 和600mA两个版本,仿真相位裕度存在了一些差别,但不是太大吧,一个是-9 一个是-17.这中间会不会存在一个临界点。

另外 原版电路的话MP1是body是接在电源的,被我改成了与MP1的源端相连,这会有问题吗?如果仿真的话,接电源的相位裕度大概只有-27还不如接源端的。

此外,如果我把输出电容从1u加大到3u,输出电压在进入限流状态后也没有发生震荡,但仿真MP2栅极断开的相位裕度,两者几乎没有变化。

断开的时候是不是应该吧MP2的Cgs添加到断点前面。

另外你说跑过流过称,是输出设成过流,在电源从0V上升到VDD跑,还是在正常工作状态下,改变负载,让电路进入限流状态。

公司就不方便说了。

QQ:253815615可以加一下,指导一下 嘿嘿

上面楼上说的都不太对.我觉得问题有两个:

(1)限流保护电路输入参考电压不能是Vout,应该是一个Vref,一个稳定的基准电压;

(2)限流保护比较器应该用迟滞比较器,此外限流电路也要加一定的迟滞,这样才不会在限流点来回振荡.

目测楼上不会LDO设计。其他不详。

相位裕度都没调好,就来仿真整体,简直浪费时间。

同意#12楼的第二点,加迟滞确实好些。

又一个菜鸟,

LDO很多芯片都是用类似结构作的限流保护,另外还起到软启动的功能。

这应该是一个比较通常的结构,我看过别人电路,在限流环路里面也没有特别进行补偿,但就是没有发生这些问题

首先,我对我发过的话表示对楼上各位表示对不起,伤到各位热心版友了。

其次,我觉得某些人说别人是菜鸟,根本没做过LDO的表示严重鄙视,我们是讨论问题,你可以说我说的不对,但是这样冷嘲热讽不会解决问题,也不利于该版的发展。

再次,我说一下我的看法:

该限流保护电路用Vout和Vg控制的电流感应电路进行比较,从而控制功率管的栅极,我觉得只是用一个快的输出电流负载感应信号和一个慢的输出感应信号进行比较,Vout是快的,比较放大器另外一端是慢的,它对输出电流负载变化慢一个误差放大器的延迟。个人感觉该电路只是够用,当然还必须按照小编的方法,在过流负载条件下对限流和主体环路进行频域仿真,调整器件参数,使得整个体系(包含多个反馈环路)的相位余度足够这是应该的,这样整体电路应该能够保证稳定;这种方法的好处是调整是连续的,但是缺点是容易不停的进入退出限流模式(如阻性负载)

但是从电路体系角度看,一般过流保护和软启动都属于大信号工作区,所以有人使用快速的比较器环路进行限流保护处理,方式就是采用Vout分压和Vref进行比较,直接关断功率管,再加以迟滞,这样就不会不停的进入退出限流区了。国外有不少芯片就是这样设计的,而且可靠性非常高。

这种限流保护电路很成熟吗?LZ能说一下哪款LDO芯片采用了这种结构吗?

亏你还是小编,严重败坏讨论组气氛,请你注意自己身份,不然可以叫别人做小编。

不是说搭一个一模一样的电路,特性就完全一样。稳定性是基本要求,肯定要做好。

说来说去不就是一个稳定性问题。既然是两个环路,居然不考虑应该设置哪个环路的带宽更大些,真是一个饭鸟

mark。

做个标记,估计过几天就会用到这个东西了

,向我对你的说的话道歉。你认为你的想法是对的你就坚持走下去吧。这个问题不会再跟你讨论的。

我在class AB 里面的限流电路和你的竟然完全一样(看来是个老电路),区别就是Rb 我用了一个电流源。

开始仿制我也发现了有震荡, 后来我加了miller compensation 在增益最大的一级的输入和输出,震荡消失。电流维持恒定。补偿电容我加在了mn1的输入和输出(GATE , drain)之间。这个电流保护环路主要增益应该在mn1这个 stage,之前的opamp 其实是个增益为1的buffer,没必要补偿。

LDO中的限流环路是小信号控制。用电阻负载测过流也不会出现进入,退出过流模式。你看到的进入,退出过流模式是因为过流时触发了过温保护,将芯片关断了。只有用大信号比较器控制过流环路才会出现进入,退出过流模式。环路中的op是钳位sense 电流管的,保证电流检测精度。这限流环路控制跟Vout无关。

我感觉我不该说明这些

之前的op是用来钳位的,利用op构成一个负反馈。但是任何负反馈环路,在不检测稳定性的前提下,就认为一个环路是稳定的。不敢这么干。而且稳定性跟闭环增益无太大关系,稳定性看的是开环,除非你画跟轨迹。

你用的运放是不是两级运放啊?