LDO输出波形疑问

时间:10-02

整理:3721RD

点击:

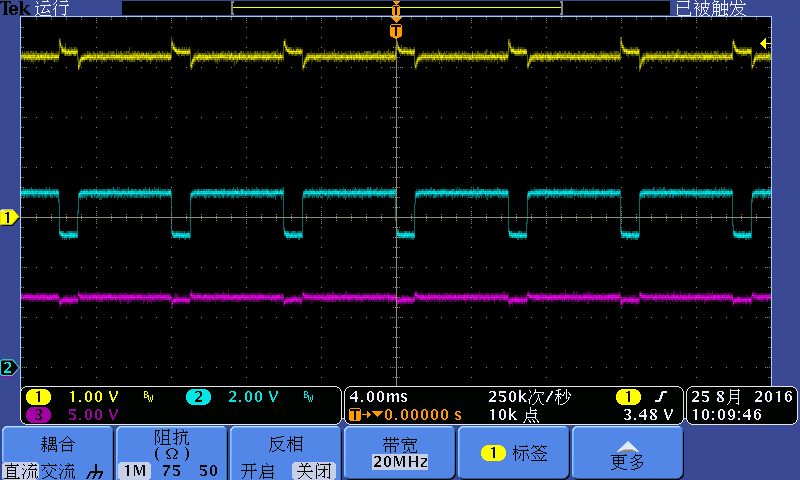

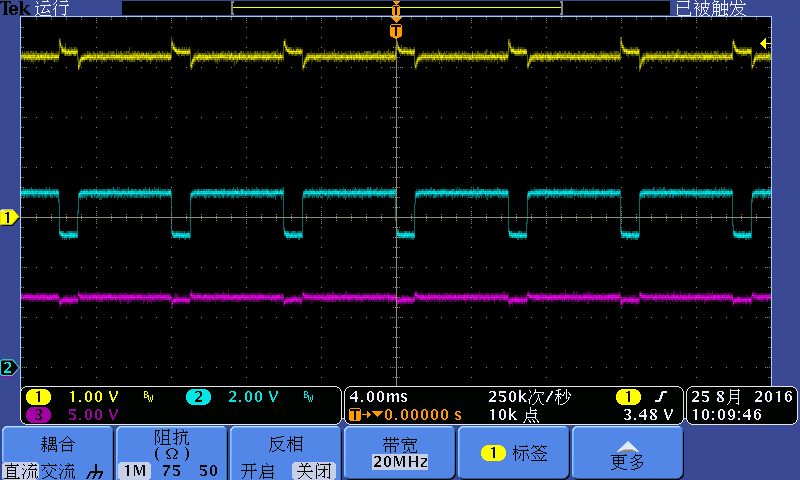

我做了一款PMOS管输出的LDO,测试时加电流负载脉冲,低电流负载20mA,持续时间5ms,高电流负载2A,持续时间1ms,测试波形如下:

其中,第一通道黄色线是LDO输出电压,第二通道蓝色线是靠近LDO端口的输入电压,第三通道紫色线是外加直流电源的输出电压。

其中第二通道和第三通道测量点只隔一条导线,低负载时这两个电压基本一致;高负载时由于线上压降较大,会把第二通道测量的电压拉低。

我疑惑的是第一通道的波形,按我的理解,在高负载时,输出电压应该比低负载时低,而测试结果恰恰相反,2A输出负载的输出电压比20mA输出负载时的输出电压还要高,该怎么解释这种现象?

请大家不吝赐教,感激不尽!

其中,第一通道黄色线是LDO输出电压,第二通道蓝色线是靠近LDO端口的输入电压,第三通道紫色线是外加直流电源的输出电压。

其中第二通道和第三通道测量点只隔一条导线,低负载时这两个电压基本一致;高负载时由于线上压降较大,会把第二通道测量的电压拉低。

我疑惑的是第一通道的波形,按我的理解,在高负载时,输出电压应该比低负载时低,而测试结果恰恰相反,2A输出负载的输出电压比20mA输出负载时的输出电压还要高,该怎么解释这种现象?

请大家不吝赐教,感激不尽!

大家都没遇到过这种情况吗?自己顶一下。

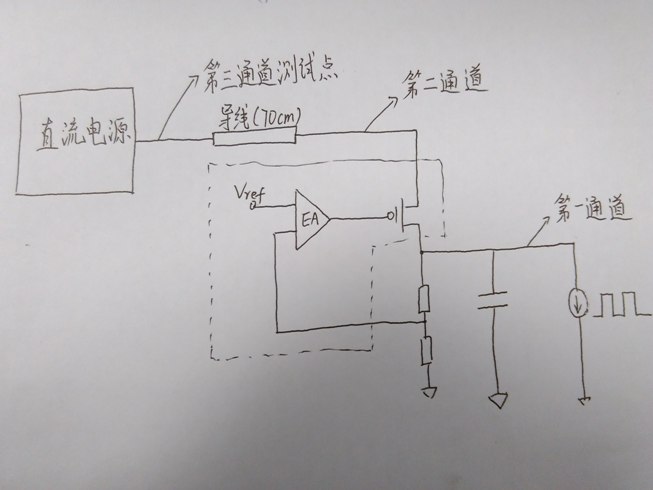

第一通道黄色线是LDO输出电压,第二通道蓝色线是靠近LDO端口的输入电压,第三通道紫色线是外加直流电源的输出电压? 小编没听懂你的意思啊,画个连接的示意图吧,这样便于分析

你的测试有问题吧,由20mA跳变至2A时,输出电压瞬间上翘了一下,这不符合常理啊。

請注意你的ground量測點, 也許在是在負載路徑上

连接方式如下:

是感觉说不通

你的意思是说,在大电流时,我现在测量点的所选定地电位,它的电压值并不是0。由于ground走线上也有线阻,在大电流时,地线上不同点的电位不同。

十分感谢,我再检查一下我的测试电路及其布线。

请再确认一下测试环境和条件,大电流情况下导线上的压降是不能忽视的。

如果以上都没问题,可能的情况是大电流引起芯片内部温度上升,请测试一下基准的温度系数是否偏正温度。

1. CH2 電壓掉1.6V, 導線電阻1.6/2=0.8Ohm, 太差的導線

2. 請問輸入電壓? 輸出電壓?

谢谢,我先按你提供的方向检查一下。

输出电压3.1V,测试时输入电压7V。

如前面所说:

1,ir drop(片内片外)

2,7v-3v,2A 负载下,8W 热对bgr的影响,使vbg抬升

3,不知道你的内部结构,看看其它模块是否出问题

4,测试环境检查

5,漏电等

测一条dc曲线吧,看你的输出和负载的关系,

感谢回复!我把你说的这几点都考虑一下,重新测试后再把结果看看。