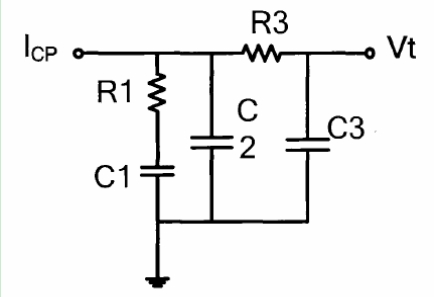

PLL 三阶滤波器 纹波1mV

,输出结果纹波很严重,约为1mV,请问具体的产生原因,相位裕度为70 deg左右,请各路大神赐教。如:零极点问题,环路带宽的问题等等。

,输出结果纹波很严重,约为1mV,请问具体的产生原因,相位裕度为70 deg左右,请各路大神赐教。如:零极点问题,环路带宽的问题等等。

补充一下,此时PLL的各个模块是用VerilogA建模的

注意UP/DOWN 電流的不匹配效應

以及charge sharing 和 feed-through

verilog A 建模,意思是前面的PFD+CP等电路都是理想的 。 1mv确实很大

此时有phase error吗?这个纹波来自哪里应该仿的出来

我猜电阻太大

检查一下up和dn current

你觉得是第三阶的过大造成的么?还是第一阶上的零点电阻

R3太大了!

三阶一般没有必要!可以从仿真看出,改进其他结构更有效果

二阶够了

当我用二阶LPF的时候,开环相位裕度仿真结果显示 对应的0dB频率处的相位裕度,并非是最大值的情况,也就是说相位裕度的最大值对应的频率点要略小于0dB处的频率点,出现这样的原因是什么,怎么修正?求指导

R1太大?

目前采用二阶的LPF

在用Cadence仿真相位裕度时,0dB频率点所对应的相位裕度不是最大值,最大相位裕度对应的频率点要稍微小于0dB点对应的频率点,出现这样的原因是为什么?怎么修正

R1和R3 还有Ipump对文波都有影响!

如果Ipump取值比较大,比如远大于10uA,甚至达到50uA以上,那么R1,R3就得小心选取

我来试试

你能否先说一下整体结构?你用dsm做fd了?干嘛要用三阶LPF?只要ref够纯净~是没有必要用3rd LPF的~而且你没有开环根图~纹波频点也不知道~问题根本没法确定的啊~

我本想是让第三阶极点处于高频处,从而抑制一些VCO的相位噪声,关于dsm和fd,大神指的是什么?小弟菜鸟。

delta-sigma modulator

frequency divider

理解。

为什么电阻大,纹波就大?通常电阻值士多少?

电阻大,纹波大

很好理解啊

dfdfdfffdsfsdfffsdfdsf