请教:奇怪的PLL Vctrl纹波

诚请各位不吝指点一二,感激不尽!

--

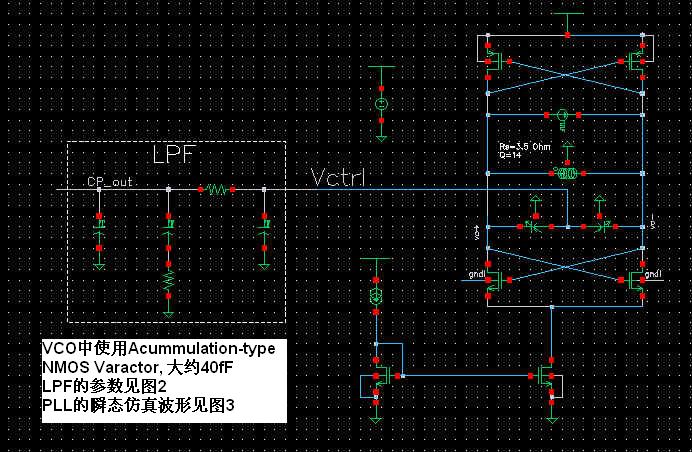

此主题相关图片如下:图1__LPF+VCO.JPG (80KB)

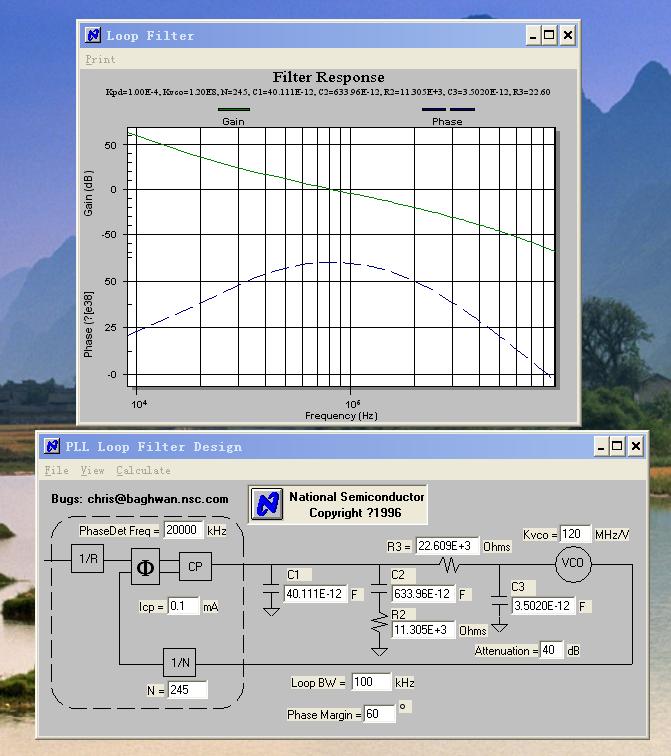

此主题相关图片如下:图1__LPF+VCO.JPG (80KB) 此主题相关图片如下:图2_PLL参数.JPG (79KB)

此主题相关图片如下:图2_PLL参数.JPG (79KB) 此主题相关图片如下:图3__VCO_output+Vctrl.jpg (160KB)

此主题相关图片如下:图3__VCO_output+Vctrl.jpg (160KB)

看不到你的图片啊

我把图加上去了,烦请大家指点,多谢!

没有问题 实际上都会有这种现象

主要是varactor的非线性造成的。正常的。该波形与交叉耦合管共源端的电压波形类似,都是二次共模波形。

恩,单个VCO是二次谐波出现在LPF上,如果是正交VCO,就是四次谐波,虽然对相噪声是有恶化的,不过似乎无法回避。

振荡时,varactor两端电压不断变化,于是,振荡波形的峰跟谷也就不对称,于是二次谐波产生,会通过varactor进入vctrl.这样会恶化Q值。

听说可以在vctrl加个电感谐振谐振,但总觉得要是输出频率变化大时不太好用。谢谢大家了!

原来是这样啊,怪不得在很多资料上看到在VCO的电流源抑制高次谐波,那么在Vcont 一般能够忍受的这种电压波动的上限一般有多大呢

控制在20mV 以内吧,越小越好

请问你的PLL是在cadence下仿真的吗?一般锁定时间要300个微妙左右,但是我仿真3个微妙,仿真数据就有10多个G了,硬盘就没有空间了,你是如何做到PLL的瞬态仿真的?能把你的proj发一份给我或加我QQ跟我联系吗?请教了!谢谢!

可以加电感电容并联谐振在2w0,形成高阻抗,防止vco输出影响vtrl....或者加电阻电容形成低通滤波器....

设置仿真器只保存你关心节点的仿真数据,数据量就小很多了,而且由于读写硬盘的次数少了,仿真速度也会提高。

hhhhhhhhhhhhhhhhhhhhh

你好,看到你对Vtune纹波的解释我受益匪浅,但是我自己认为可能不是那个原因,我觉得尽管可变电容会变化,但是VCO的两端的差分输出也是同时变化的,所以波峰与波谷的位置还是应该对称的,这样基波成分在Tune上的叠加应近似为0了,只是二次谐波成分可能会叠加到Vtune上,但是这样的2w频率比较高,不会影响杂散指标,因为他影响的杂散在2W处,应该远在带外,但是如果幅度过大的话,可能会影响可变电容的变化,这样就可能会影响频率的变化,这样就会影响相位噪声,但是也是在带外,所以不比关心,我们所关心的是低频的干扰(带内),我有个问题就是带内的杂散大家是怎么分析的,一般鉴相器工作频率在几M以上时参考杂散就可能在带外,对指标影响不大,但是带内还是要有杂散的,怎么样减小呢?

你好,看到你对Vtune纹波的解释我受益匪浅,但是我自己认为可能不是那个原因,我觉得尽管可变电容会变化,但是VCO的两端的差分输出也是同时变化的,所以波峰与波谷的位置还是应该对称的,这样基波成分在Tune上的叠加应近似为0了,只是二次谐波成分可能会叠加到Vtune上,但是这样的2w频率比较高,不会影响杂散指标,因为他影响的杂散在2W处,应该远在带外,但是如果幅度过大的话,可能会影响可变电容的变化,这样就可能会影响频率的变化,这样就会影响相位噪声,但是也是在带外,所以不比关心,我们所关心的是低频的干扰(带内),我有个问题就是带内的杂散大家是怎么分析的,一般鉴相器工作频率在几M以上时参考杂散就可能在带外,对指标影响不大,但是带内还是要有杂散的,怎么样减小呢?

感謝經驗分享

这个问题我刚好也遇到了,正好来eetop上找解决方法。我认为,振荡电压就算是完全对称的,由于二个可变电容瞬时的二端电压不一样,可变电容的瞬态电容不一样,这样相对于震荡信号来说阻抗不一样,震荡信号叠加后也不会出现随时间不变的效果,这也就导致了Vctrl上纹波很大。刚做过实验,可变电容越大,瞬态电容差就越大,Vctrl上纹波就越大,且和可变电容成比例增加