RAZAVI书中相位裕度的问题

应该不是,源跟随器做输出时经常会出现这种情况,在高频下输出阻抗会增大,类似于电感,因为M5的Cgs把源和栅极短路了。Razavi 6.3节讲得很清楚

eeeeeee

ddddddd

25

很不错

大有志者事竟成

xssseeee

恩,很好

FOUNDING......

我不同意上面的回答。

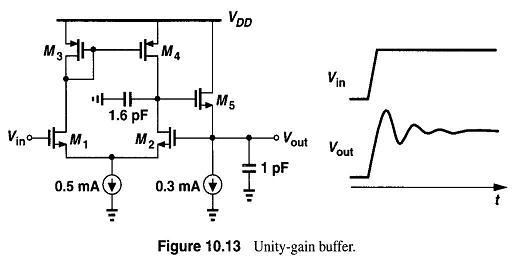

拉扎维说得已经很清楚了,在大信号的情况下,偏置电流和电压处于过渡状态,和小信号状态下分析相位余量的工作点是不同的,这是一个非线性的时域过渡问题,这种情况下零点和极点并不是小信号稳态情况下的零点和极点,所以就算小信号分析时得到了65度的相位余量,还是应该从时域分析中看一看电路对大信号的响应。

如果要考虑M5的Cgs,那么座小信号分析时候早就应该考虑过了。另外电感效应在GHz以上才有效应,这里的Unity Gain Buffer怎么会到GHz呢?

别把问题想得太复杂了,把自己绕进去了,这里面本身没有什么mystery.

同意楼上的看法,我认为主要原因是non linearity导致pole和zero的变化。

感谢sewan的捧场,所见略同!

分析的精彩。

Razavia在6.3节中最后说明原因。

比较同意amodaman和sewan_1看法。

曾经在仿真全差分运放的建立的时候碰见过类似问题,而我仿真的运放并没有采用源极跟随的输出。

高手

学习了~

好,谢谢!

对,6.3节讲的是小信号推导,与P291给出的解释不符。

我觉得这个电路有这种结果在于那个1.6pF的电容。

M5这级的随着频率升高增益下降,Cgs5等效到1.6pF节点处的电容值自然也随着频率升高增益下降,因此该节点电容值变化,估引起极点位置变化。

如果没有1.6pF的电容,该节点的极点应该在高频处,那么他的变化对时域响应影响就不大了。

有兴趣可以去掉这个电容仿下电路。大信号响应在PM=65deg情况下应该很漂亮了。

个人拙见

学习了

顶AMODAMAN

进来看看

:)

近来学习一下子

我覺得只是電流太大~小一點應該就不會有這個現象

受教受教,不错

hm.. it looks very hard.. sorry

1# gibsonmpf

学习学习。