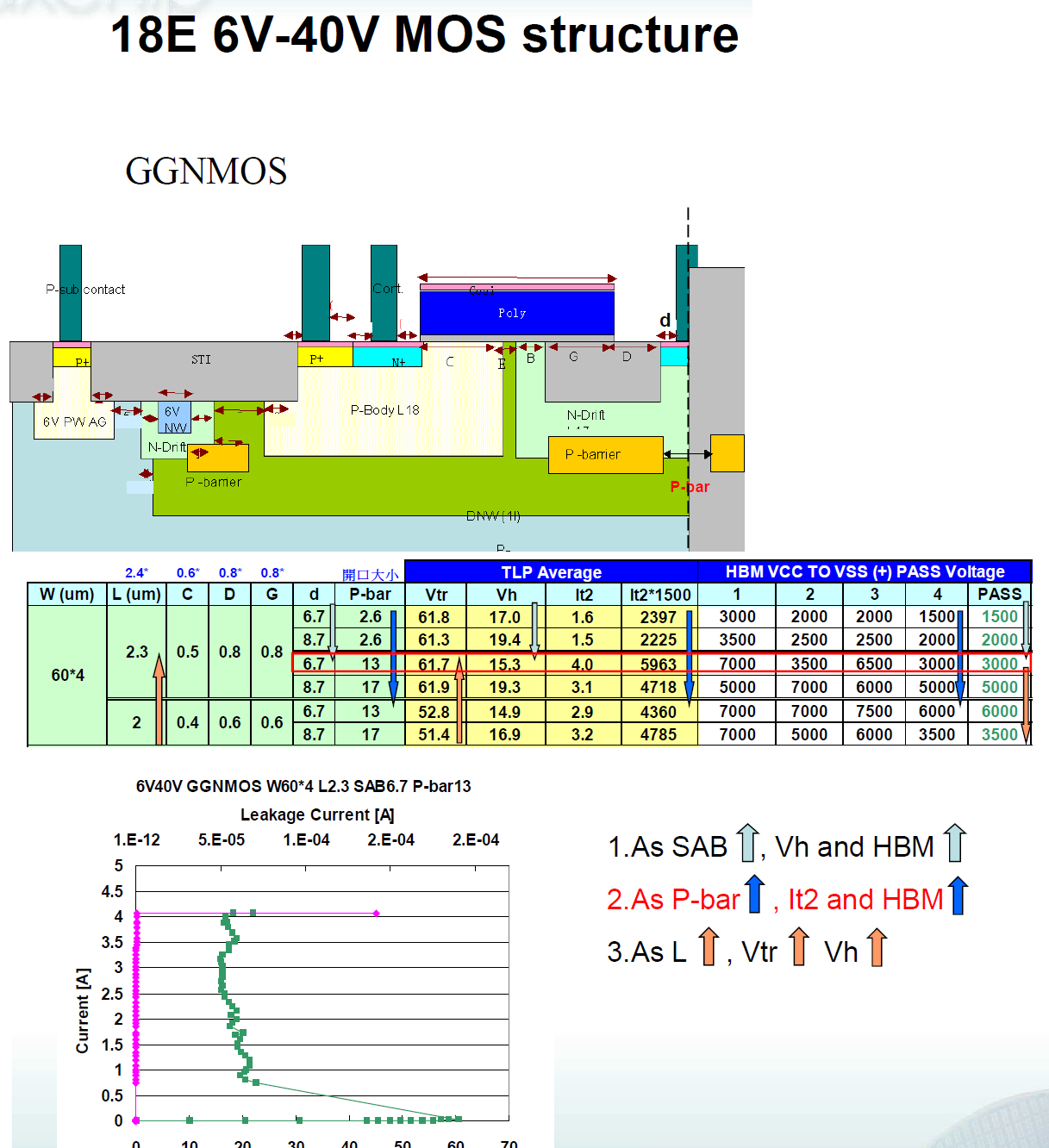

GGNMOS P barrier 为什么能提高ESD能力!

时间:10-02

整理:3721RD

点击:

RT,小弟最近在用某工艺40V平台,发现其有个参数是P barrier的距离,P-bar越大,ESD能力越强,不太明白其作用,希望各位指点一二,欢迎讨论。

另外,小弟电路里面唯一用的40V器件是一颗耗尽型LDMOS,尺寸为200*40/4u,面积很大,觉得这个端口可以不用做ESD,请问如何来评估?

见过一次20V ISO LDNMOS不用ESD,宽度105mm,VGS=10V的1um旧工艺。

5V标准工艺见过的不用ESD的NMOS尺寸是15mm/0.5um

15mm,好大。不知道这个您是怎么评估后得出不用做ESD呢,感谢

这是常压DC-DC的常用尺寸,例如NMOS 15m + PMOS 35m,高压的LDNMOS估计面积要求会更大,要做好风险评估

加入Pburry后,电场由以前的单一的横向电场变为横向和纵向电场共同作用。

1、削弱了表面电场

2、增加了纵向的击穿区域,增大了电流通路

最不好的就是单纯的表面横向的击穿,电场太集中,击穿薄弱,抗电流能力差。

你可以用一个器件仿真,看看有埋层和没有埋层的情况最大电场和击穿电流的通路就了然了。

您说的是有无pbarrier是Resurf效果是吧?但是图中这个pbar是两个pbarrier的距离,拉大是增加了Resurf的效果吗?我去查一下?感谢您

就是不知道怎么评估风险啊,,求指导个思路。

个人觉得200*40/4u的面积太小了,有很大的风险,因为LDMOS的ESD一向是难点,面积需求比普通MOS大很多

没有太精确的方法来评估,你可以做TLP仿真,看实际的峰值电压/电流有多少,然后根据经验来评估。