请教一个LDO低频PSRR的问题

system offset导致的

能不能具体点,这么大的增益系统offset应该很小,再说系统offset是如何影响低频PSRR?

还有就是,系统offset基本上不随电源电压变化,而是随负载变化

你可以先用个简单点的电路,结合理论研究下system offset和PSRR。搞明白后你就知道了

你电路的system offset是否随电源电压变化,要看你的电路结构,能给出来么?

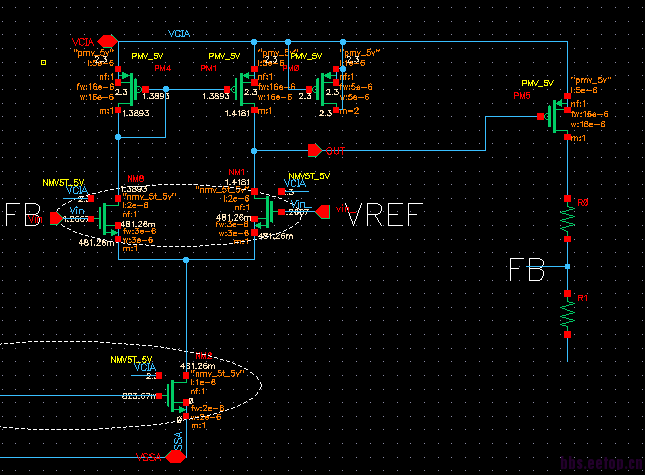

就是这样一个简单的结构

电源会影响这个电路的system offset的。你再把PSR为40dB,70dB时候的电路节点电压图分别给出来。我看下。

你可以做以下尝试:调整电路,尽量让system offset 电压很小。然后在上面的两种电源电压情况下分别看下PSR是否也会有很大差别。

你给我的图中的静态点就是你出问题情况的电路的静态点把?也就是有一定的system offset,但是电源电压变化不会使该system offset变恶劣,这是你说的电源电压不影响offset的变化。

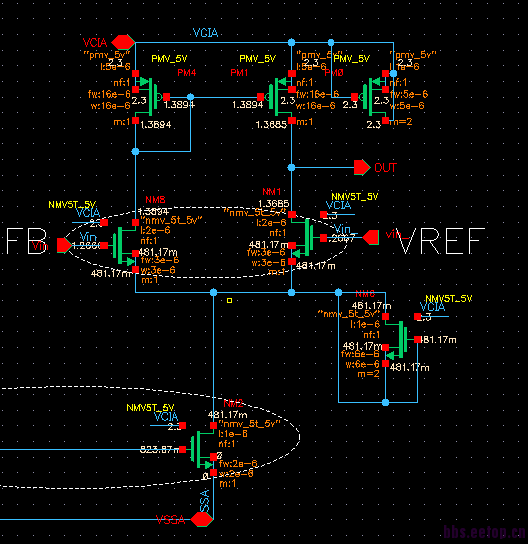

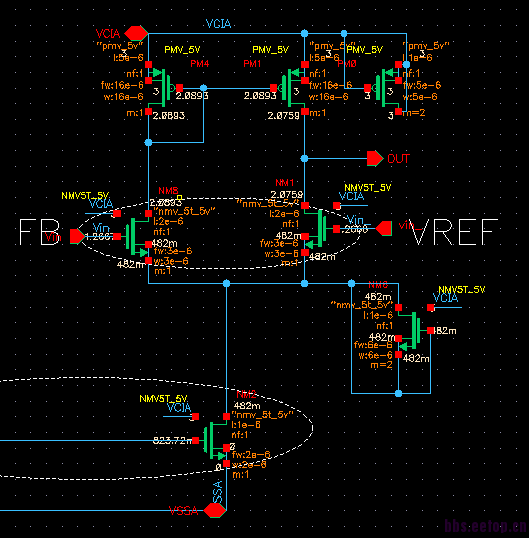

70dB 静态工作点

70dB 静态工作点

我调整了系统offset,对PSRR没有任何影响,能不能把你说的系统offset对PSRR说具体点。

怎么具体?我只有定性的结论,没有定量的数据。看来跟system offset没关,我猜你仿真psr激励加错了吧,你确定下。

能不能说下,系统offset跟PSRR的关系?

系统offset越大,psr越差,CMRR越差。

你VREF電壓是怎麼給的?

是電阻分壓或是用BANDGAP?

若是VREF這點PSRR低

即使AMPLIFIER環路增益非常高

整體PSRR還是會由VREF的PSRR來決定

请问下,40dB,70dB 是指的放大器增益还是环路增益?

环路中除放大器之外其他部分电路的静态工作点呢?

问题找到了么?基准电路PSR会对主体PSR有影响,但关系不大。

电源电压变化 会导致offset变化很大吗?以前倒是没有注意

能否指出 对于哪些常见的结构 会有这个类似的结论?

如果小编说的是运放的增益,则有可能LDO工作在低压差下了,导致的环路增益不够。

我覺得是轉的輸出電壓不同造成的結果

该结构在低频下的PSRR严重依赖于POWER管的VGS电压,在电源电压降低时,由于输入管的gds变大,POWER管GATE端电压不在严格跟随VDD,所以PSRR降低

能具体说一下吗

pfet moves to linear region when VDD drops, there is not much attenuation from VDD to Vout, so PSRR drops. That is also the drawback of using pfet as power fet....

楼上正解

学习学习