请教输出可调LDO的PSRR的问题

时间:10-02

整理:3721RD

点击:

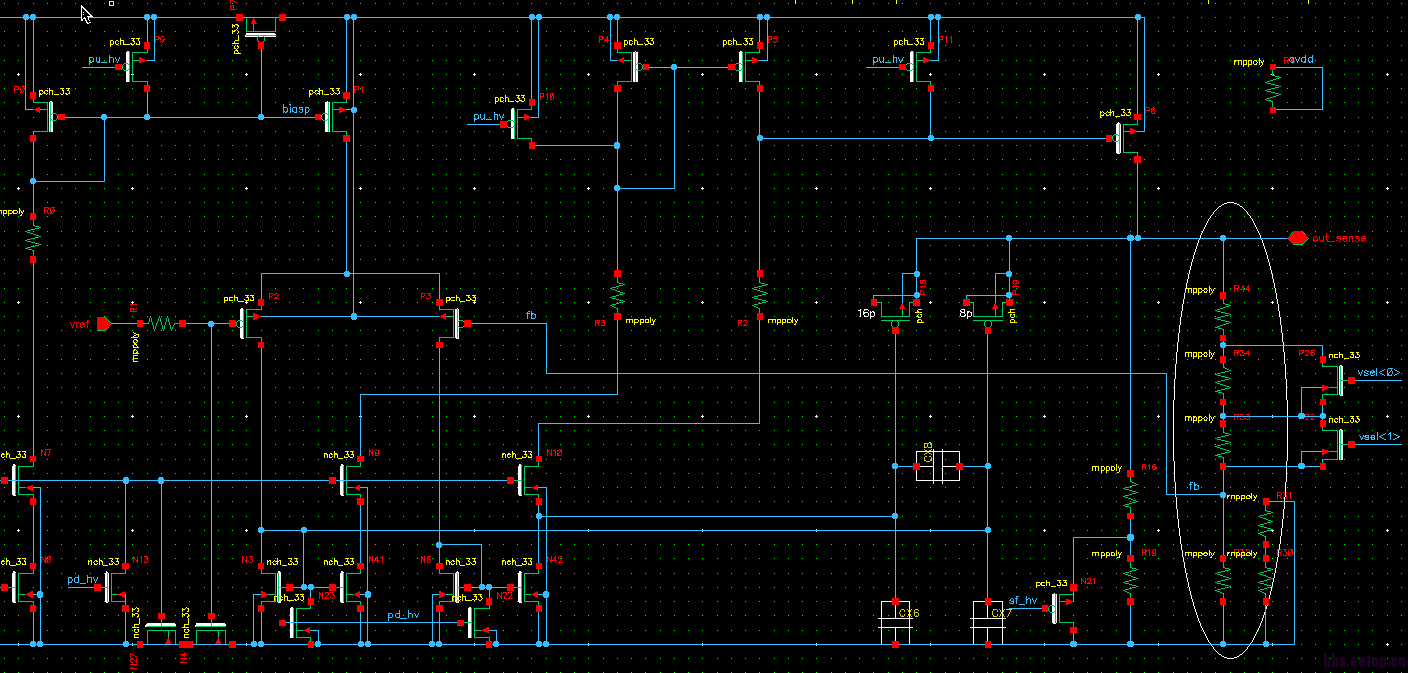

这是设计中采用的ldo的结构,因为要输出不同的电压所以通过开关选通电阻控制输出电压。有两种选择,一种是衬源连接的NMOS管,如图

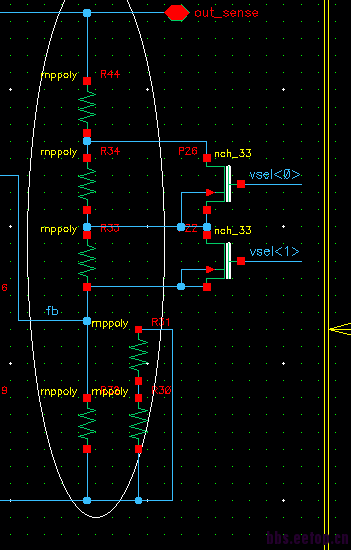

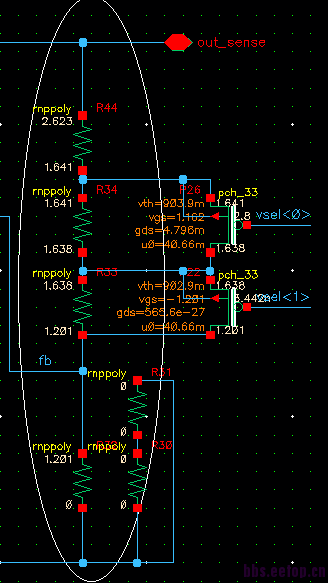

这是设计中采用的ldo的结构,因为要输出不同的电压所以通过开关选通电阻控制输出电压。有两种选择,一种是衬源连接的NMOS管,如图 。一种是衬源连接的PMOS管,如图

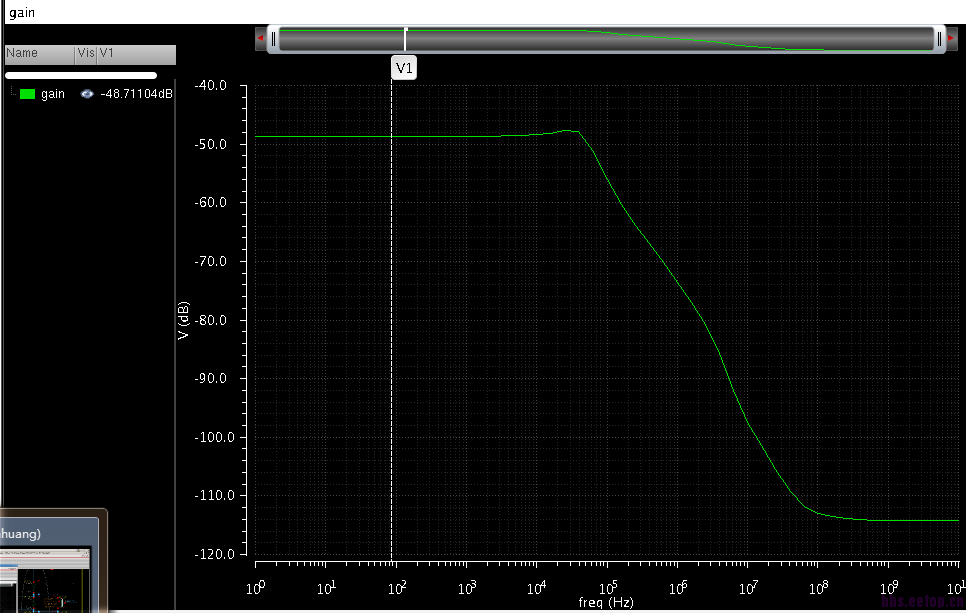

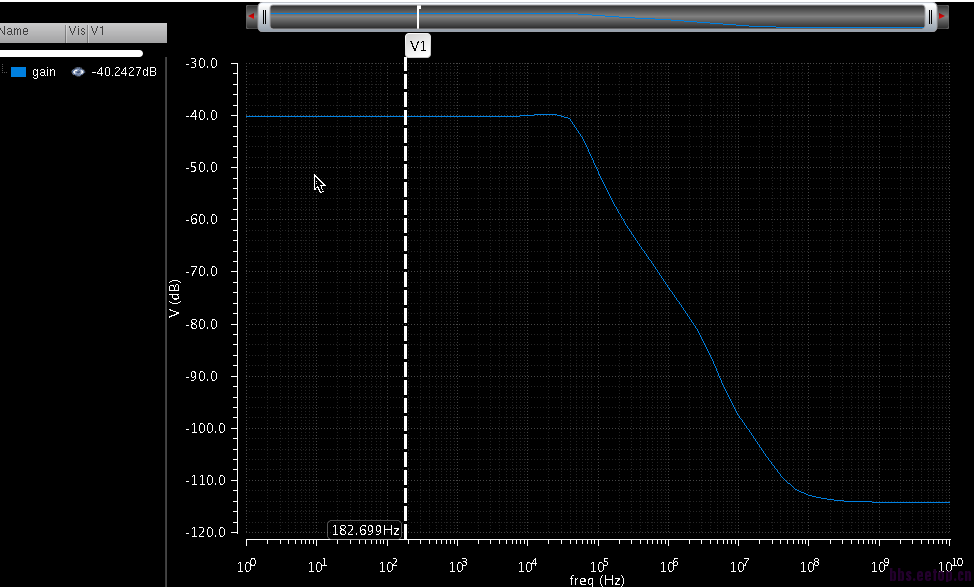

。一种是衬源连接的PMOS管,如图 。此外还有衬源连接的CMOS开关。采用衬源连接的原因在于该工艺阈值电压比较高,接电源或者地导通电阻太高。分别采用三种开关的PSRR仿真结果为

。此外还有衬源连接的CMOS开关。采用衬源连接的原因在于该工艺阈值电压比较高,接电源或者地导通电阻太高。分别采用三种开关的PSRR仿真结果为

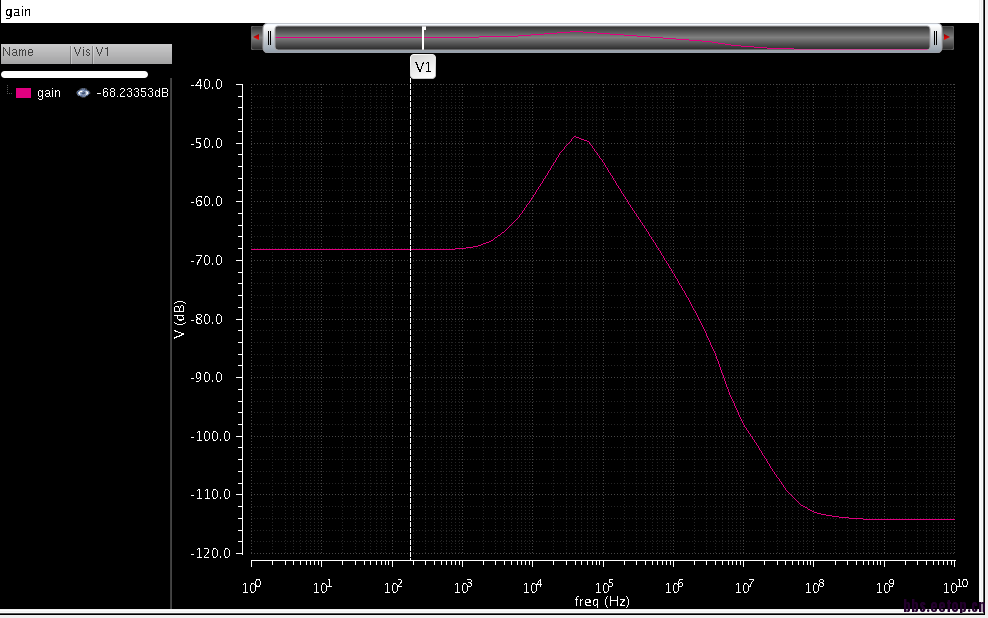

,结果中PMOS开关的PSRR为68dB,NMOS开关的PSRR为40dB,CMOS开关的PSRR为48dB。从导通电阻来说,三个开关的导通电阻都足够低,但是为什么采用PMOS开关的PSRR会远大于其他两个?第一次发帖,诚心求教,困扰数天没结果了。

,结果中PMOS开关的PSRR为68dB,NMOS开关的PSRR为40dB,CMOS开关的PSRR为48dB。从导通电阻来说,三个开关的导通电阻都足够低,但是为什么采用PMOS开关的PSRR会远大于其他两个?第一次发帖,诚心求教,困扰数天没结果了。

自己顶一个。

可不可以这样考虑,选通的电平,PMOS管为地,NMOS为电源,而仿真PSRR时多用的是电源?小编试一下仿真地的PSRR,看看结果有否不同?

尝试仿过地的PSRR,NMOS开关和PMOS开关相差不多。之前我也曾经尝试过,将第一级运放用理想运放代替,结果三种开关的PSRR基本一致。但是实际电路中却出现这样的结果,实在是费解啊。

NMOS开关:低频段,线性区的导通电阻与Vgs相关,反馈回去的电压与VDD相关高频段,Cgs耦合

應該是主電路架構+開關的影響

最好先看看NMOS开关那样接能不能实现

实际工作中,你的电路不能这样单纯地把source 和 bulk接在一起。

可以那么接,工艺中有深N阱,在深N阱中可以实现NMOS衬源相接。

已经解决。原因应该跟你说的一样。如果NMOS开关的控制电压直接给理想电压,而不是来自跟电源相关的反相器提供的电压,电路的PSRR不会降低。万分感谢。

提高PSRR,有没有什么好的办法?