Cadence veriloga理想DAC相关问题

时间:10-02

整理:3721RD

点击:

相关代码:

module dac_12bit_ideal (vd11,vd10,vd9,vd8,vd7, vd6, vd5, vd4, vd3, vd2, vd1, vd0, vout);

electrical vd11, vd10, vd9, vd8, vd7, vd6, vd5, vd4, vd3, vd2, vd1, vd0, vout;

parameter real vref= 5 from [0:inf);

parameter real vtrans= 0.75;

real out_scaled; // output scaled as fraction of 4096

analog begin

out_scaled = 0;

out_scaled = out_scaled + ((V(vd11) > vtrans) ? 2048 : 0);

out_scaled = out_scaled + ((V(vd10) > vtrans) ? 1024 : 0);

out_scaled = out_scaled + ((V(vd9) > vtrans) ? 512 : 0);

out_scaled = out_scaled + ((V(vd8) > vtrans) ? 256 : 0);

out_scaled = out_scaled + ((V(vd7) > vtrans) ? 128 : 0);

out_scaled = out_scaled + ((V(vd6) > vtrans) ? 64 : 0);

out_scaled = out_scaled + ((V(vd5) > vtrans) ? 32 : 0);

out_scaled = out_scaled + ((V(vd4) > vtrans) ? 16 : 0);

out_scaled = out_scaled + ((V(vd3) > vtrans) ? 8 : 0);

out_scaled = out_scaled + ((V(vd2) > vtrans) ? 4 : 0);

out_scaled = out_scaled + ((V(vd1) > vtrans) ? 2 : 0);

out_scaled = out_scaled + ((V(vd0) > vtrans) ? 1 : 0);

V(vout) <+ transition( vref*out_scaled/4095, 0, 0, 0 );

end

endmodule

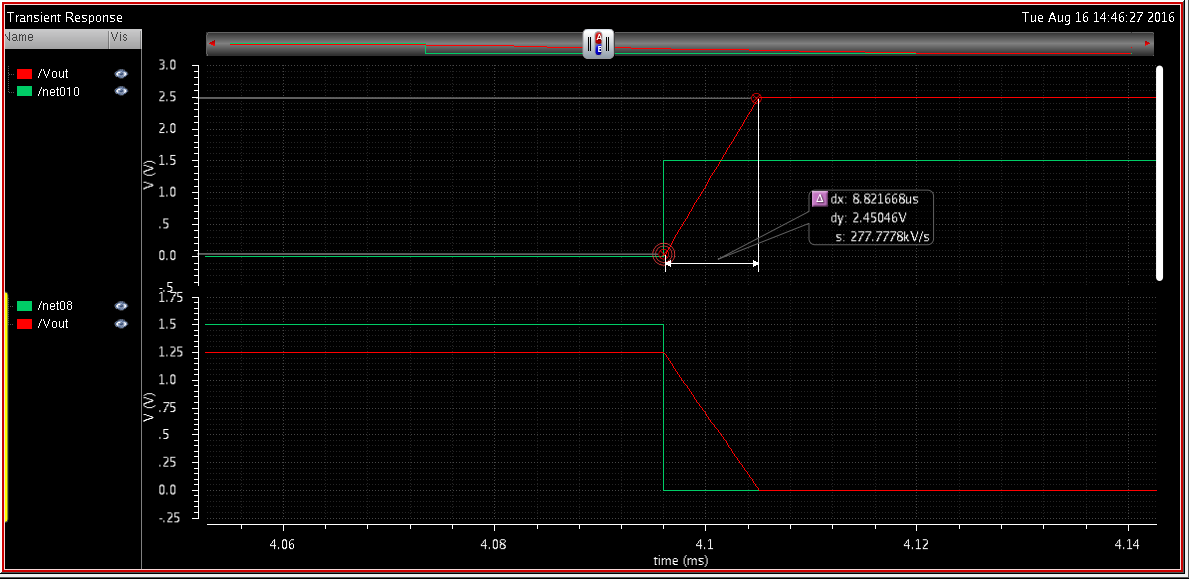

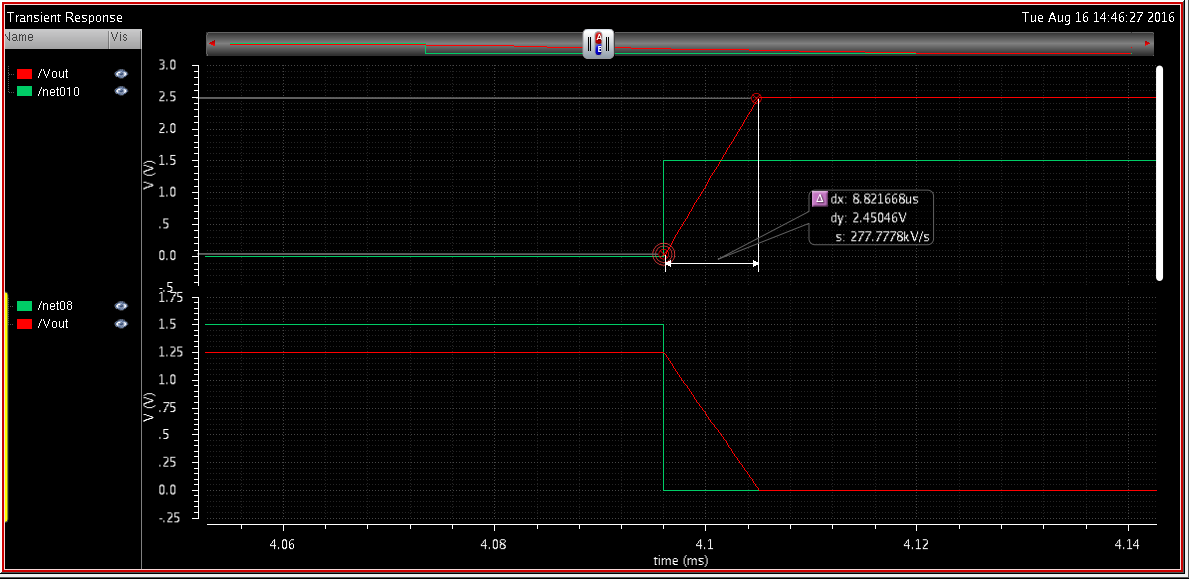

问题:输出信号vout的rising time & falling time 均设为0了,为何仿真出来后,输出的信号仍然有接近9us的延时?不应该是立刻响应嘛,起码也不会比控制信号的延时多那么多。

附图:

module dac_12bit_ideal (vd11,vd10,vd9,vd8,vd7, vd6, vd5, vd4, vd3, vd2, vd1, vd0, vout);

electrical vd11, vd10, vd9, vd8, vd7, vd6, vd5, vd4, vd3, vd2, vd1, vd0, vout;

parameter real vref= 5 from [0:inf);

parameter real vtrans= 0.75;

real out_scaled; // output scaled as fraction of 4096

analog begin

out_scaled = 0;

out_scaled = out_scaled + ((V(vd11) > vtrans) ? 2048 : 0);

out_scaled = out_scaled + ((V(vd10) > vtrans) ? 1024 : 0);

out_scaled = out_scaled + ((V(vd9) > vtrans) ? 512 : 0);

out_scaled = out_scaled + ((V(vd8) > vtrans) ? 256 : 0);

out_scaled = out_scaled + ((V(vd7) > vtrans) ? 128 : 0);

out_scaled = out_scaled + ((V(vd6) > vtrans) ? 64 : 0);

out_scaled = out_scaled + ((V(vd5) > vtrans) ? 32 : 0);

out_scaled = out_scaled + ((V(vd4) > vtrans) ? 16 : 0);

out_scaled = out_scaled + ((V(vd3) > vtrans) ? 8 : 0);

out_scaled = out_scaled + ((V(vd2) > vtrans) ? 4 : 0);

out_scaled = out_scaled + ((V(vd1) > vtrans) ? 2 : 0);

out_scaled = out_scaled + ((V(vd0) > vtrans) ? 1 : 0);

V(vout) <+ transition( vref*out_scaled/4095, 0, 0, 0 );

end

endmodule

问题:输出信号vout的rising time & falling time 均设为0了,为何仿真出来后,输出的信号仍然有接近9us的延时?不应该是立刻响应嘛,起码也不会比控制信号的延时多那么多。

附图:

给自己顶一个,寻大神指点

将上升时间和下降时间改一下看看。不知道可不可以直接设置为0.

设置时间后,的确可以,就是不知道为啥设置成0的时候默认会有那么大rising time ,估计cadence中不存在0 rising time这种状态,毕竟同一时间表示了两个不同的值