电源抑制比的问题!

哈哈,GND上的噪声对psrr的影响是很大的哦,尤其是P管输入的Miller OTA

of course not。

芯片不会是只有你一个模块的,现在大都是soc,所有的片上模块的地都是通过bonding线拉出来(或者downbond出来)到外面的地,

再通过via和片外别的模块共用一个ground。由于电阻电感效应所以你的ground离真正的ground还差得远呢。

呵呵,补充楼上的,其实看实际应用。比如做motor controller,电机一转起来,搞不好整个芯片就down了

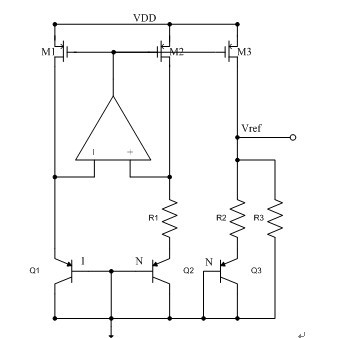

我问这个问题是因为我看到带隙基准中,输出电压那一段下面都是直接接个电阻,都谈不上电源抑制了

谢谢您的解答,你给看看楼上我追问的问题吧

谢谢!麻烦您能再看看我楼上追问的问题不!

不知道你做的chip地线有多差?做了不少bandgap,都只是仿了VDD psrr,实测也没什么问题。地线不干净,还真不知道有什么招,难道用twin power supply?

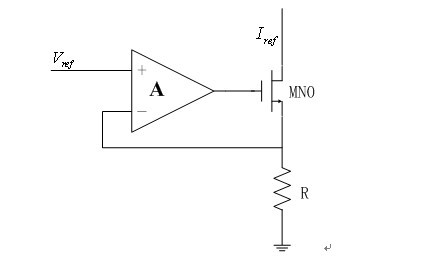

我也问的是这个问题,地应该比电源稳定,但是前面人回答的是一定要care地的影响,但是你看哪个buffer,地上的噪声直接到输出的。

学习了!

我也想知道答案谢谢

拉扎维那书写的电源抑制比说的是电源对输出的影响,我的理解是那个电源是把地给理想化的。所以在实际考虑电源抑制比的时候应该也是把地的变化给考虑进来的。

干吗一定要地clean,

尽最大可能保证地线的干净,也就说,芯片内所有与VSS连接的节点到PCB板地线的寄生阻抗最小。

有人说,地线是微波电路的"生命”。应该进一步,地线是电路的“生命线”。

地线电平是参考,当然PSR只需要看电源的性能。如果以电源电源为参考的话,地线的PSR需要考虑。

zwtang

2012/8/18

看到你的电路了,单纯来看这块电路,这样的BG确实对GND上的noise几乎没有抵抗力。

我个人认为哈,关键是你的BG和其他电路在layout上共地情况是否恰当,因为你输出的稳定电压本质上是电压差,即Vref-V(bg’s gnd),这个是相对恒定的,保证bg的gnd和其他电路gnd尽量一致,你的Vref就没有太大的电源抑制比问题了。所谓的BG电路的PSRR一般只仿真Vdd端到Vref的PSRR,其实隐含了前提条件:BG电路和其他部分电路共地良好。这不是仿真保证的,而是layout以及制程来保证的。

有咋好的办法解决这种问题?

电磁干扰引起的?

同学。

这得具体电路具体分析了,没有一个固定的说法。bg的输出在dc下一定是针对自己局部的地了。但是他的输出被后一级如何使用情况又不一样。假如后一级是个buffer,再假设两边的地dc下有差异,那么就要看buffer的输出需要针对谁而言了。如果buffer的输出需要针对buffer的地,那么bg的地(相对于buffer的地)变化就等价于buffer输入的变化,buffer的地变化是没有讨论意义的。如果buffer的输出需要针对外部另一个地,那么bg地(相对于外部地)的变化等价于buffer输入的变化,buffer地(相对于外部地)的变化等价于负psrr的影响。这还只是dc下情况的讨论,在ac下,电容起到主导作用,电容如何放置又是一番问题。这些情况在现实电路中都有可能发生。其实如果能正确画出电路,分析的方法只需要最基本的分析技巧,但是难就难在把实际的情况转成电路图。这也是差分比单端有优势的一个重要方面。我推荐adi的几份针对ground的application note,讲的比较清楚。

至于优化方法,如果能所有的地保证完全一致,那自然就没什么可讨论的了。但有时候这种理想情况并做不到。那时候把各个地尽可能短接?有时候似乎并不是最好的方法,因为我曾经看到有人举出了一个例子来反驳,也看到某个仪器并没有这么做。这也是我一直想知道答案的问题。

这位说的比较靠谱,单纯对一个模块来说,局部ground足够low impedance,所有电压track ground至少对自己来说就够了。用local bypass+r 和star connection可以避免由于共地bonding wire的影响,不共地模块用differential也能解决ground pollution的问题。

其实也不是不可以仿真啦,带上package模型和别的电路一起仿真,可以评估,只是可能会比较慢。

上面大家的讨论都很对,讨论问题确实必须针对应用背景啊,手机里的芯片,所有的地其实最后都refer到拿着手机的人体到大地,如果是医疗电子里的微弱信号检测,信号是uV级别,可能答案又不一样。

小编能提出这个问题说明自己是会思考会主动性的,很多答案你可以自己根据你的应用背景,通过做一定的仿真来得到一定的结论。

前面说的仿真方法里,比如你的bondwire电感比如跟旁边的某个clk信号的bondwire有互感。你仿真发现只有k值低于某个水平时才不会对噪声产生比较明显的contribution(在最恶劣的corner下)。最后可能的结论是,此bondwire线临近两根线都必须是别的bond wire地线才有可能屏蔽掉这个问题。当然我们最后可以说,哦这是显然的嘛,就跟我们射频电路的pin周围不会立刻放大规模数字电路的pin一样。但是只有通过仿真得到一定的data,你才对你的芯片有自信对吧:)

长文兄? 高手!

学习,学习。

请教一下啥是twin power supply啊?为什么采用这个就能抑制地的噪声了呢

学习了

用local bypass+r 和star connection可以避免由于共地bonding wire的影响

大侠这句话是什么意思 ?望不吝赐教

学习了

gnd

用磁珠?

!

如何去分析电源抑制比呢