关于SD-ADC的SNR偏小问题

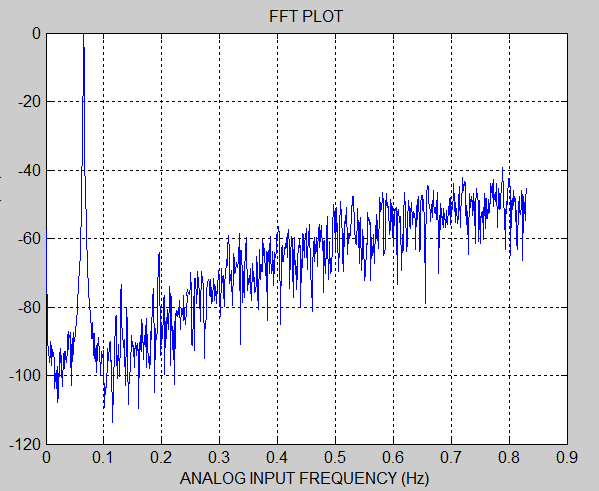

,求大神帮分析问题是出在哪里。根据图像感觉DC部分的噪声翘起来了,不知道原因在哪里。

,求大神帮分析问题是出在哪里。根据图像感觉DC部分的噪声翘起来了,不知道原因在哪里。

ADC的输出有没有减去平均值?

matlab的code里已经减去输出的平均值了啊,应该没有DC信号的

你要么贴的详细点要么别贴,没意义

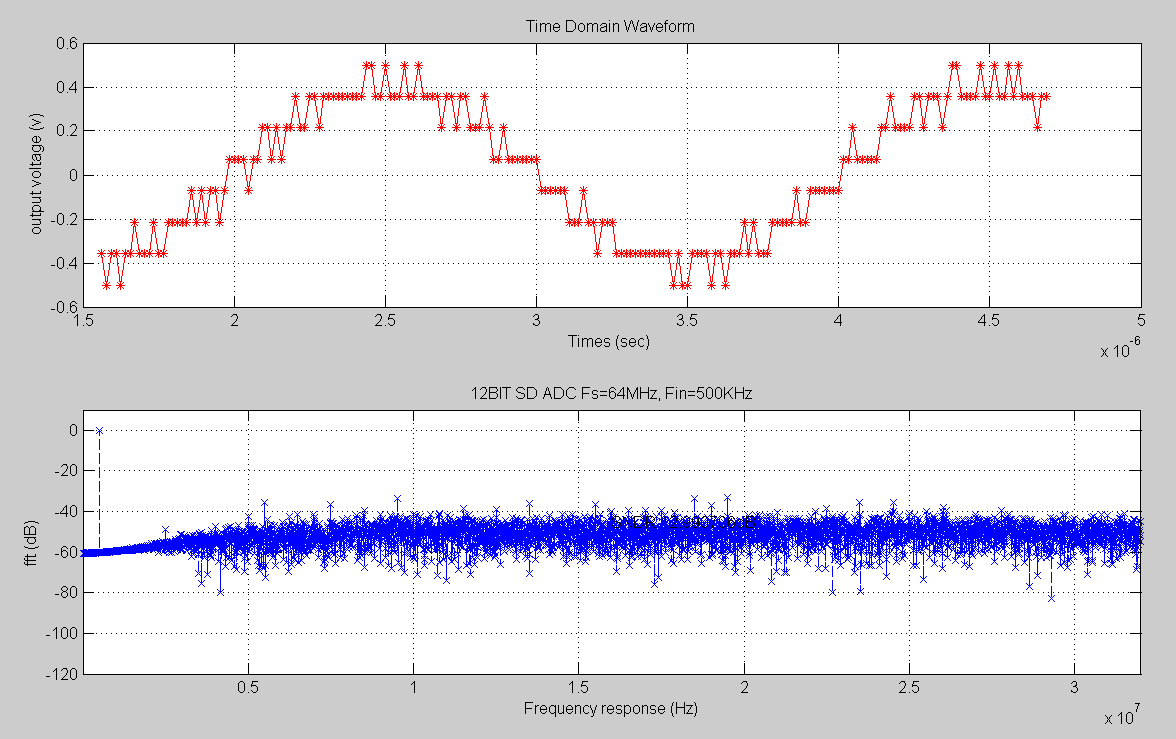

不好意思,因为刚接触的modulator,我也不知道还需要哪些信息。我做的是连续的SD modulator,3阶滤波,8位量化。matlab建模仿出来是84dB,我查了一下,前馈和反馈系数都没错,反馈DAC是电流反馈,怕这个地方有问题,我把DAC换成理想的电流源反馈了,结果SNR还是13dB,现在真的不知道是哪个地方出问题了。难道是量化器的延时太长引起的?Matlab仿真的系统容忍延时可以达到3n秒的,我量化器的延时不到0.4n。顺便附上恢复出来的时域图像,不知道有用没有

我再补充下,刚才的确发现DC附近的噪声有上翘,请问这可能是由哪些原因造成的?[attachimg]492554

有取window吗?

还有你的信号频率是怎么取的?

取window了,输入信号500K,FS=64M,OSR=32

感觉你的DAC有问题,你做了DWA了吗?

而且,输入信号和采样率看起来没coherent,hanning winow? 三个点就该下来了。

我查了下代码,原来是取噪声bin的时候忘记除以OSR了,除完之后SNR是60dB左右。我已经做了DWA了,反馈DAC即使用理想的电流源反馈,SNR也只能达到61dB,还是比预定值小了很多。现在发现前面的2个bin噪声很高,如果从第三个Bin开始计算,那么SNR就能达到70多dB了。请问DC附近bin的噪声可能是由哪些原因引起的啊?

我加hanning了,不过我不懂你指的coherent是什么意思?能麻烦讲一下吗

试试做2048个点的FFT,然后输入频率取 64M/2048*161 = 503.125kHz ,看看结果怎么样。

还有个问题不是很清楚,就是信号能量bin是取哪几个,是取[Fin-1,Fin,Fin+1],还是取[Fin-2,Fin,Fin+2]?这两种取法我在不同的代码里都看过,两种取法我的SNR差了有7个dB,现在真的不懂选哪种

我取加减一的,前提是输入频率和采样率的关系对。你原来那个频率选择,感觉有点问题

问题有点意思。可能是FFT点数太少了,有些信号能量泄露到噪声BIN里面了。

建议使用65536点FFT分析。

看你FFT的结果,怎么也不止16dB的SNR啊!

找到问题的所在了么?我现在遇到这个问题了 想请教一下

仅从PSD图看, 存在明显的频谱泄露!

看频谱图感觉SNR不会这么低,你算信噪比不会把带外的也算进去了吧- -

请问一下LZ的DWA是在哪里建的模型?