各位PLL的大神,帮忙分析下我仿的几个曲线

时间:10-02

整理:3721RD

点击:

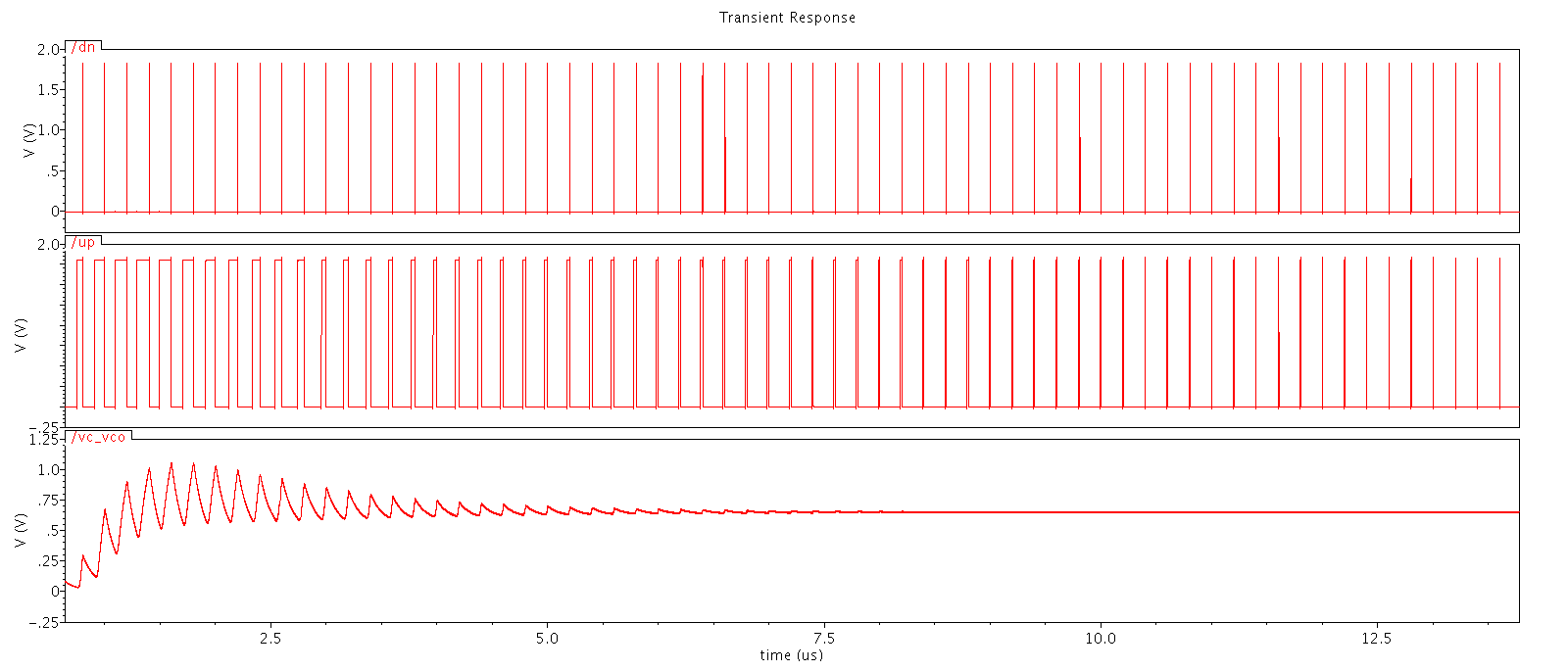

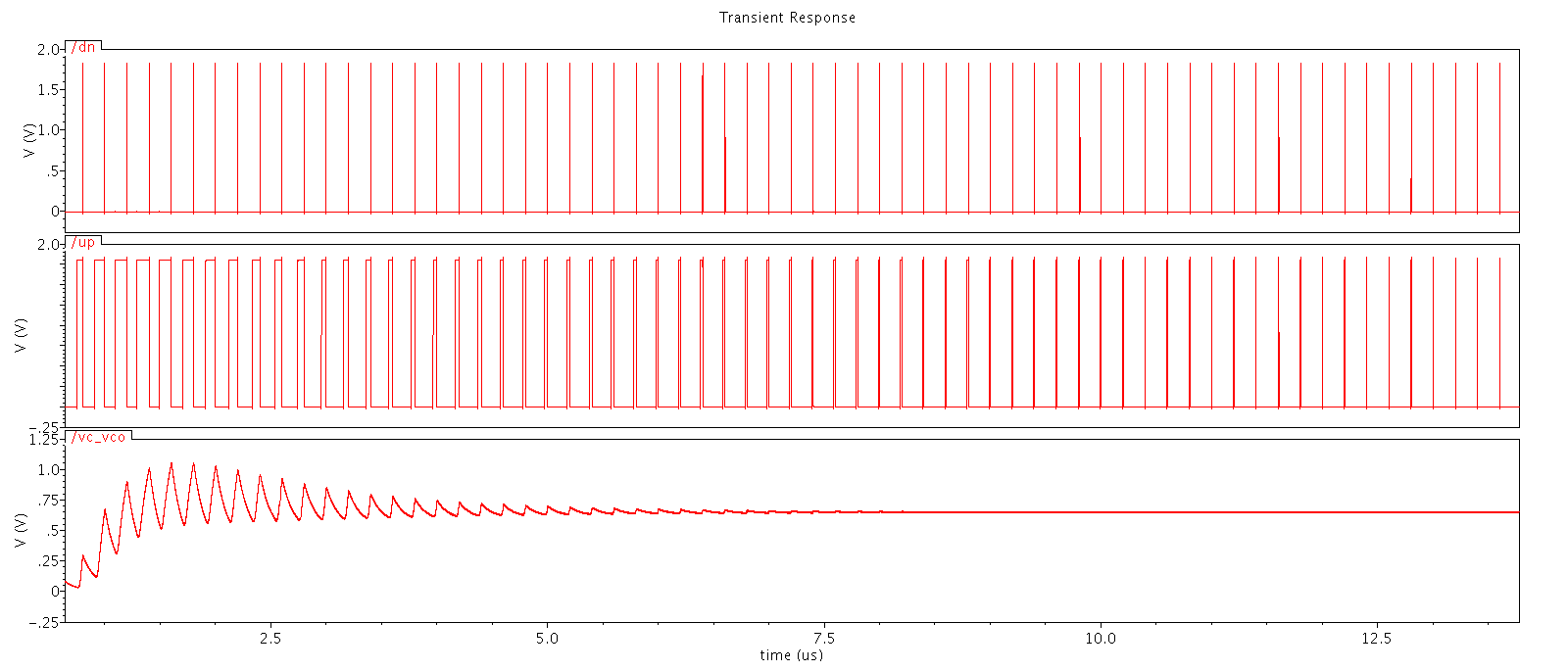

下面几张图是我仿真的pll的瞬态,整体图为

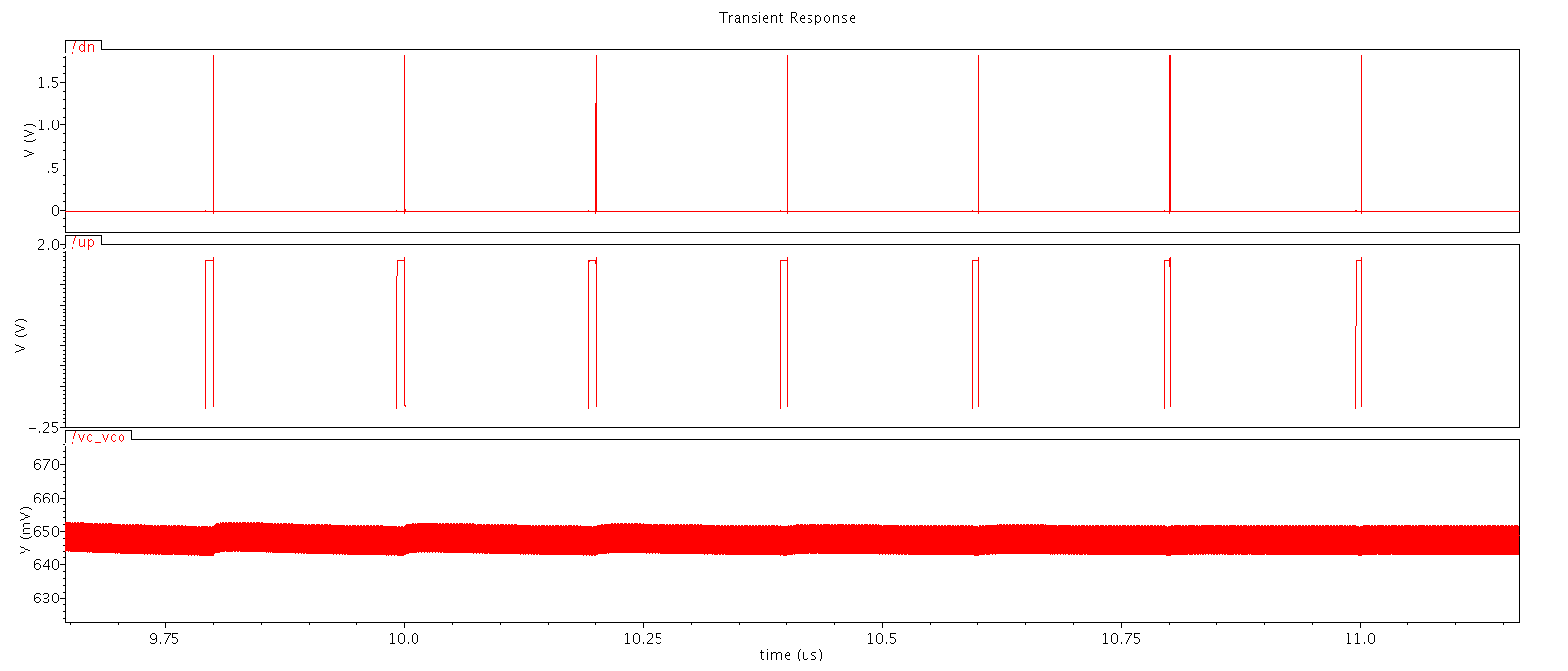

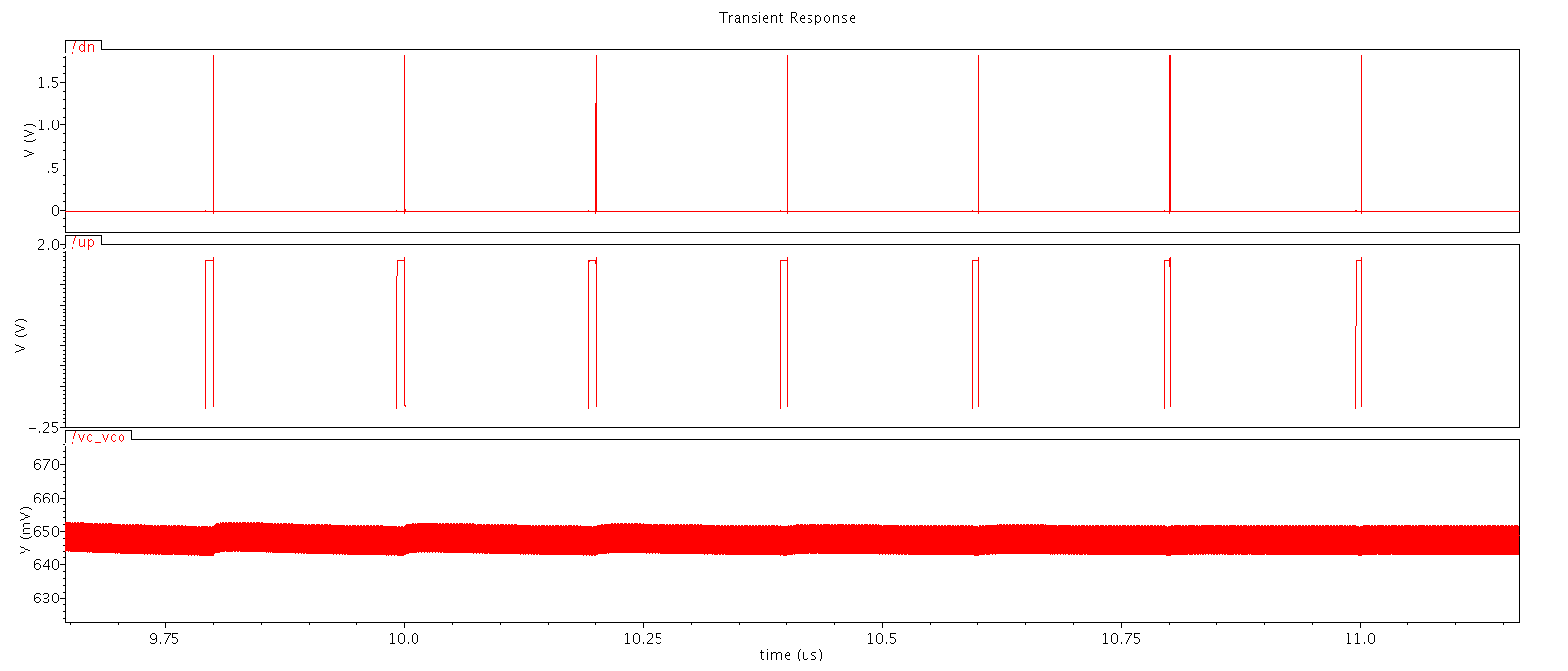

在控制电压稳定之后,进行局部放大,分别有up有一定剩余相差

在控制电压稳定之后,进行局部放大,分别有up有一定剩余相差

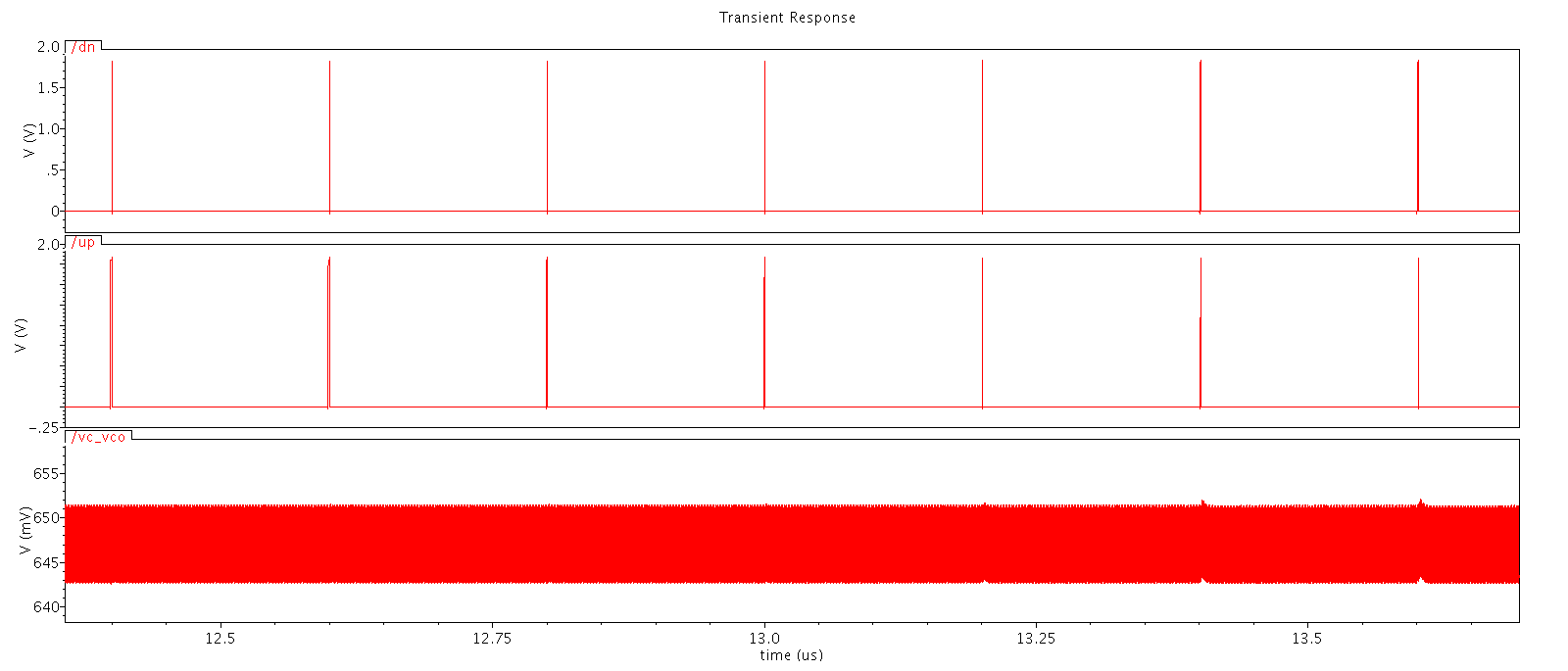

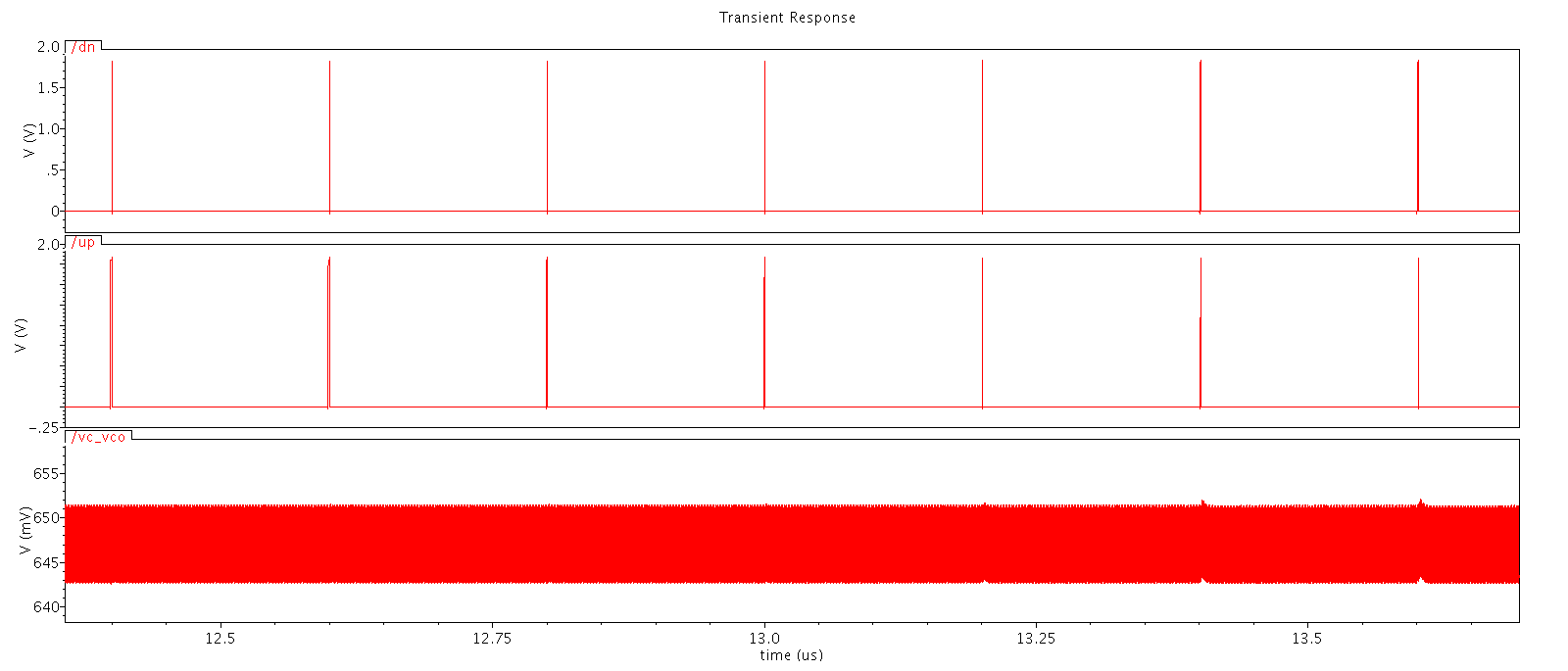

up和dn基本无相差

up和dn基本无相差

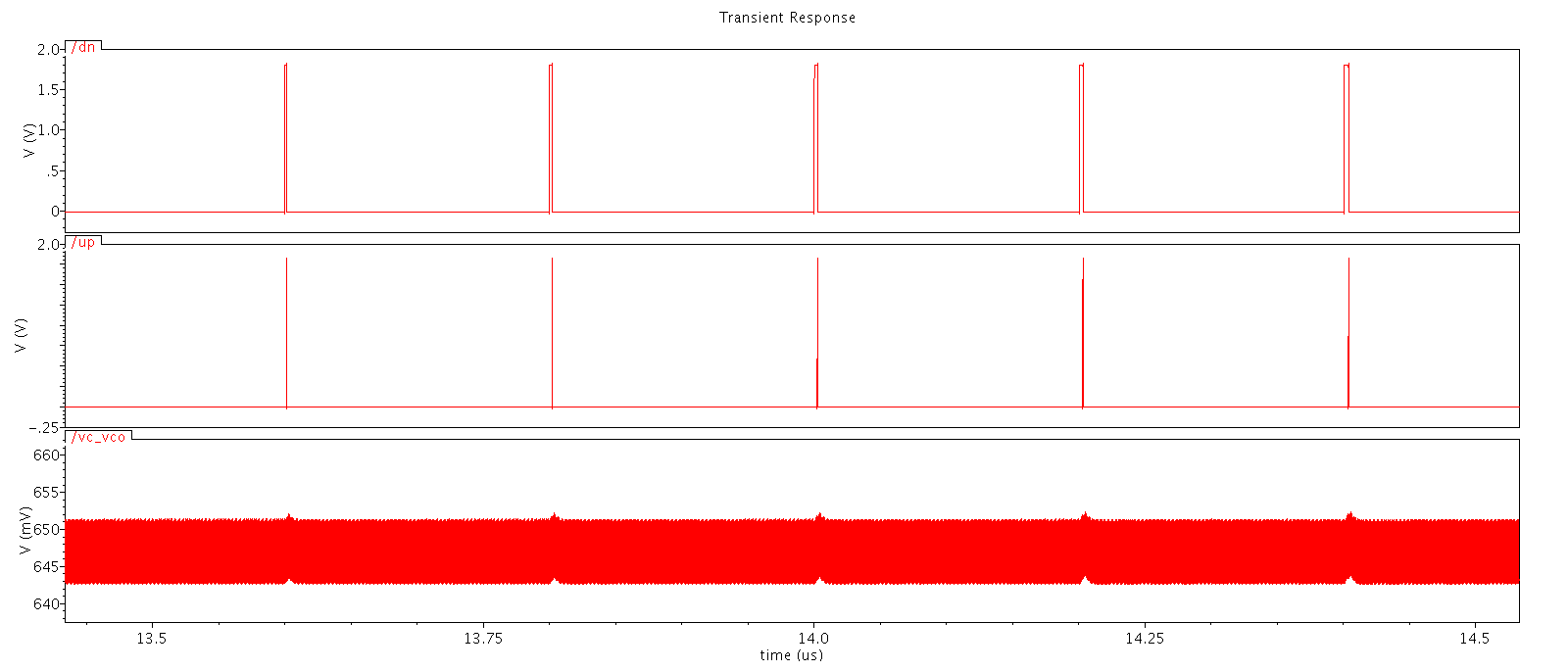

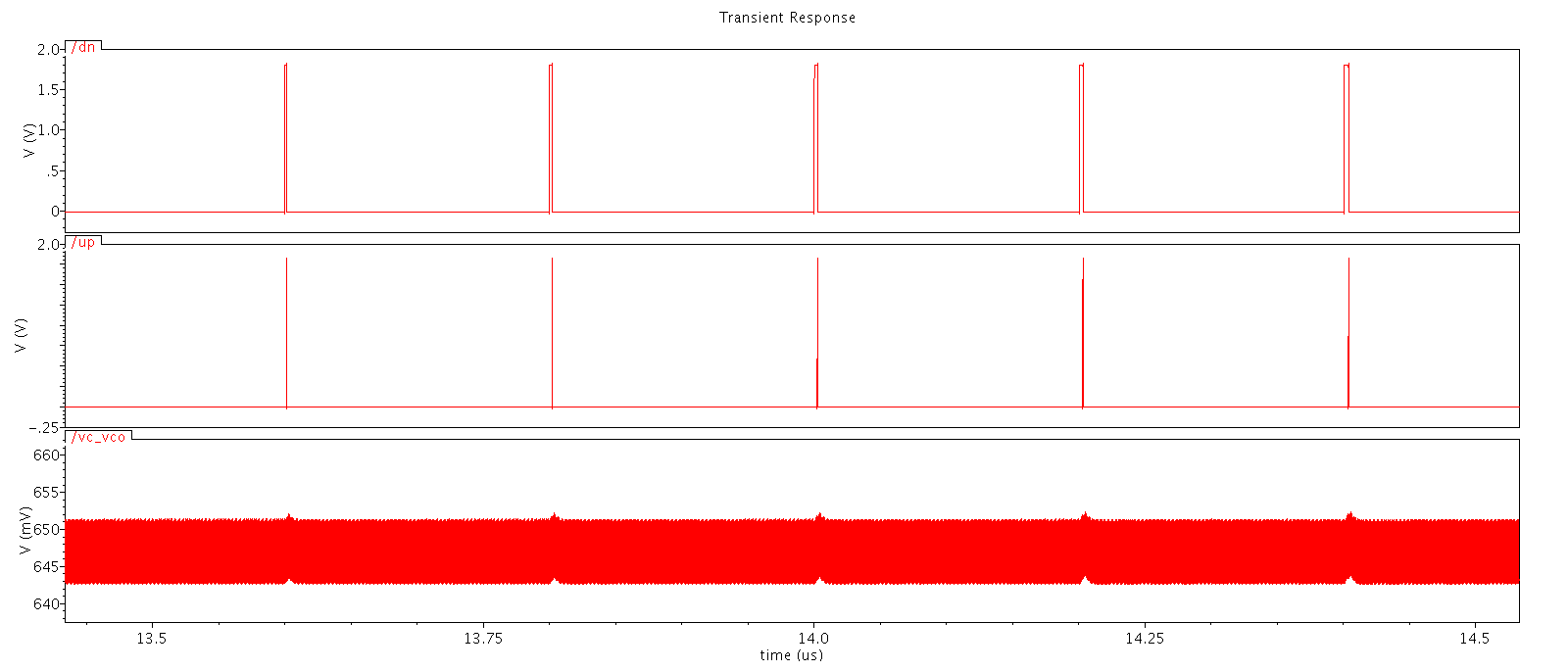

到dn有一定相差

到dn有一定相差

,我的问题是:up和dn这种交替的出现一定相差就是稳态相位误差吗?这种情况是正常的吗?一般稳态相位误差多大算正常,还有就是我VC的波动有差不多10个mV,有时仿真也只有几百uV,这种vc的波动和什么因素有关?

,我的问题是:up和dn这种交替的出现一定相差就是稳态相位误差吗?这种情况是正常的吗?一般稳态相位误差多大算正常,还有就是我VC的波动有差不多10个mV,有时仿真也只有几百uV,这种vc的波动和什么因素有关?

在控制电压稳定之后,进行局部放大,分别有up有一定剩余相差

在控制电压稳定之后,进行局部放大,分别有up有一定剩余相差 up和dn基本无相差

up和dn基本无相差 到dn有一定相差

到dn有一定相差 ,我的问题是:up和dn这种交替的出现一定相差就是稳态相位误差吗?这种情况是正常的吗?一般稳态相位误差多大算正常,还有就是我VC的波动有差不多10个mV,有时仿真也只有几百uV,这种vc的波动和什么因素有关?

,我的问题是:up和dn这种交替的出现一定相差就是稳态相位误差吗?这种情况是正常的吗?一般稳态相位误差多大算正常,还有就是我VC的波动有差不多10个mV,有时仿真也只有几百uV,这种vc的波动和什么因素有关?

ripple太大可能是因为你的环路带宽太大了吧

我的环路带宽给的400K左右(输入参考频率5M)这个环路带宽算大吗?环路带宽小纹波就小吗?

我自己顶下,别沉了

你这个VC上的Ripple频率很高啊,是不是VCO馈过来的?

ripple有点大哦,我才做了一个,ripple只有10几个uV

PFDCP有dead-zone吧?

请问死区会造成较大的ripple吗?我不知道我的PFD+CP有没有死区,要怎么看呢?谢谢啦

看有没有死区,只要关注UP和DOWN信号有没有共同的开通时间即可。

有死区的CP比较好。

环路带宽小,会抑制参考杂散,就是频率为Fref的纹波。不过从图看,你的纹波频率显然不是参考频率啊,你把横坐标拉开看看,是不是VCO振荡频率。

有死区的比较好吗,我怎么看到好多文章的努力是去消除死区的呢

有道理,如果稳定后稳态相差比较大和那些因素相关呢

纹波的大小与filter的两个电容有关系。PFD需要一定时间的死区,这样能避免up/dn脉冲太短不能打开PC的开关。

tran的step是多大?VCO输出的tran jitter有多大?

如果足够小,那么不用管

PFD的延迟大小要足以消除死区,而且CP的充放电电流要尽量匹配

我觉得你说得是不是有点问题,应该是PFD要有一定的延时来消除死区,保证电荷泵能打开,而不是说要有一定的死区时间吧

TRAN的maxstep是100p,tran仿真用eye diagram 看的是254ps,好像还挺大的

我不知道怎样看延时是不是比我的死区时间大,如果说我CP的两个开关打开的速度不一样,是不是也会造成稳态相位差较大呢?谢谢您