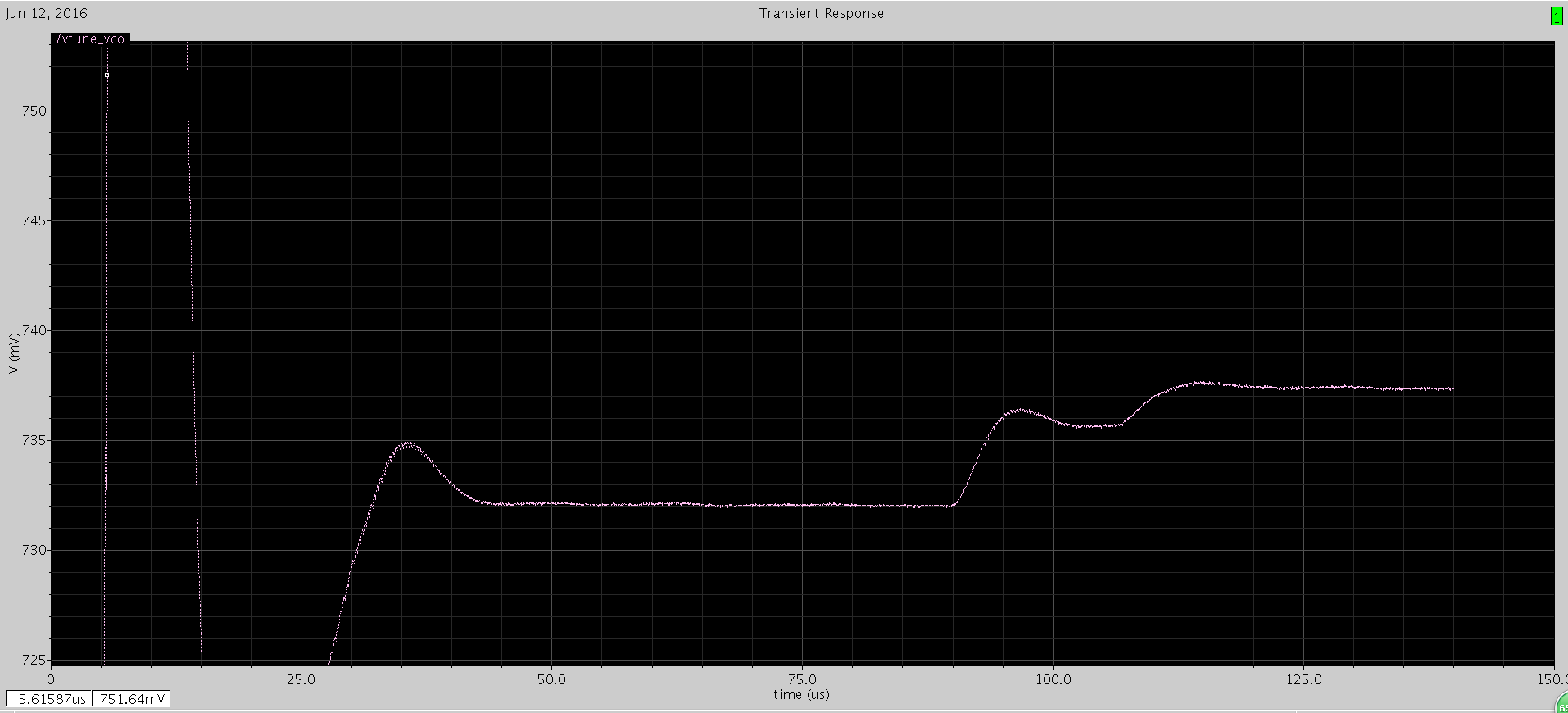

pll锁定时VCO的控制电压

我根据什么判定pll是否已经锁定了呢?

表示很奇怪,仔细查看一下电路吧

是查看各模块的环路参数是不是合理,还是查看各模块的功能是否正确呢?

90us那边是不是改变了环路的某个值,比如分频器?

没有啊,环路参数都是设定的固定值,并不是阶跃之类的信号。

同关注,会不会和仿真精度设置有关?

我的VCO输出频率3GHz,tran步长设置的0.1ns仿真精度就算有影响,也不该这么大吧?

pll鉴相频率是多少?是否设置了锁定电压的范围?

鉴相频率是指PFD的输入频率吗?这里是3.2M。设置锁定电压的范围又是什么意思啊,请指教~

这样一个周期只有三个点,会不会精度不够?

那很难解释这突变了

LC VCO,当它的控制频率的电压Vt有范围限制的时候可能出现这种情况。你们用的是LC VCO吗。若不是,我就不知道了

没错,是LC VCO。不过控制电压怎么会有限制呢,应该是0~Vdd都能调节的呀?

我觉得应该还好吧,之前也仿过,也没出现这种情况~

LC VCO的频率,是用电容阵列扩展的,电容阵列是由数字电路控制的,每更改一次数字,是有一个频率的,从图看大约为60us,VCO的频率控制电压,可以采用为0~VDD,但是,当电压为0或者VDD附近的时候,Kvco会变化比较大,另电流失配也会比较大,通常只取中间一段电压范围

大概要仿真等电压稳定超过60us,才可以认为PLL已经稳定了

没错,我们用的的确是电容阵列的LC VCO,4位控制位产生16条调谐曲线。不过我仿真的时候控制字都是固定的,当前控制字对应的调谐曲线是包含所需频率的。也就是这个过程中并不存在不同曲线之间的跳变...

有没有前辈知道这是怎么回事呢,这几天被这个问题卡了好久了

Check loop bandwidth?

您的意思是vtune的突然跳跃是由于这个时候环路带宽突然发生了变化吗?比如?

是不是VCO后的负载loading 效应或者VCO的电压pulling?比如VCO 的LDO的输出电压正好在这个地方有变化?

环路带宽多少?