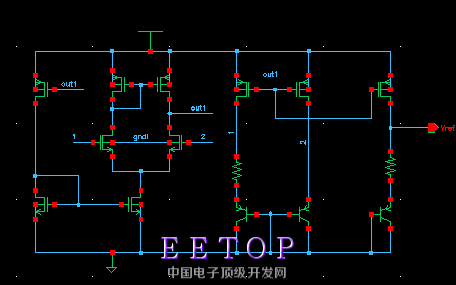

设计一个增益为80DB的单级折叠式共源共栅运放

时间:10-02

整理:3721RD

点击:

这是一个折叠式共源共栅运放结构,用的smic.18的工艺,用到了p18,n18,p33,n33这些mos管,电源电压为3.3V。(要求做到高psrr增益为80db以上)这个运放是用来放在带隙基准电压源结构的。但是对这种运放的整个工作不怎么懂,不知道怎么设计管子宽长来达到80db的增益,把恳请各位大神帮帮忙解释一下这个运放的原理。还有能不能具体的教教我怎么设计它的尺寸。

这是一个折叠式共源共栅运放结构,用的smic.18的工艺,用到了p18,n18,p33,n33这些mos管,电源电压为3.3V。(要求做到高psrr增益为80db以上)这个运放是用来放在带隙基准电压源结构的。但是对这种运放的整个工作不怎么懂,不知道怎么设计管子宽长来达到80db的增益,把恳请各位大神帮帮忙解释一下这个运放的原理。还有能不能具体的教教我怎么设计它的尺寸。

顶上去

谢谢啊

1000rmb,我可以帮你做。

结构已经有了,我觉得就是计算的问题吧?

Bandgap 不要用这种结构,高增益带来你的noise会很大。

个人理解,运放需要放在反馈回路中,psrr才更明确一些;

如果是用在带隙,感觉80dB的增益没有太大的必要吧?我倒是觉得运放+反馈环采用高psrr结构,offset做小要重要一些;

就是计算不知道从何入手。第一次设计这种。

加补偿呢?

noise和补偿没有关系。

而且PSRR要求80dB的话(低频),你的放大器做到40dB就够用了。

我之前做了一个50db的运放,但是电路的psrr只有60db,提不上去啊

我只要999,你要的是4位数,我只要3位数

貌似这个带隙的工作点设置有点问题;

你的psrr怎么仿真的?PSRR=Av(from differential)/Av(from supply). 还是PSRR直接等于AV(from supply)

输入是交流1V,输出就是psrr了吧

PSR 加两级Regulator不就可以了。你的bandgao自偏置部分没有filter,那是正反馈,要小心。

有啥方式降低bandgap的noise吗?

你可以把三支路改为两支路,把输出从2再加个电阻引出

正常PSRR的测量方式是先找到differential mode的gain在找到gain from power supply到output的。所以你要问清楚你们是怎样定义80dBPSRR的。我猜测是规范定义的。如果只是在supply上加一个交流1V的话,你测出来的gain应该是个负数。

尝试过这种方式,可是结果一直调不出来。