行为级DAC波形不理想,怎么修正,求助!

时间:10-02

整理:3721RD

点击:

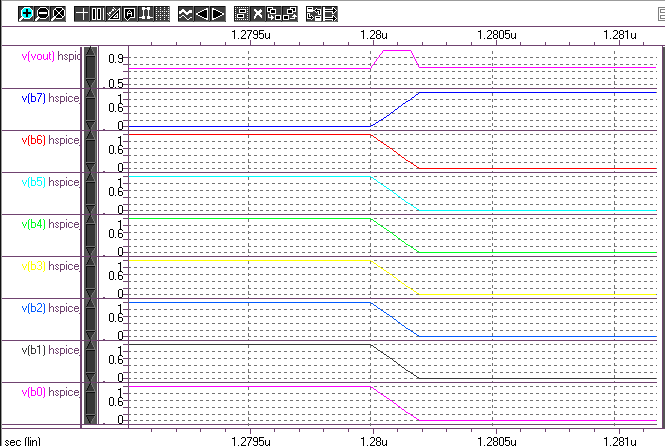

输出本应是严格阶梯状的,出现在在输入信号上升下降时

下面是网表

- ****Start ideal 8-bit DAC Subcircuit************************************

- .subckt DAC8bit VDD VREFP VREFM trip Vout B7 B6 B5 B4 B3 B2 B1 B0

- *Change input logic signals into logic 0s or 1s

- X7 trip B7 B7L Bitlogic

- X6 trip B6 B6L Bitlogic

- X5 trip B5 B5L Bitlogic

- X4 trip B4 B4L Bitlogic

- X3 trip B3 B3L Bitlogic

- X2 trip B2 B2L Bitlogic

- X1 trip B1 B1L Bitlogic

- X0 trip B0 B0L Bitlogic

- E1 VOUT 0 VOL='(v(VREFP)-v(VREFM))/256*(v(B7L)*128+v(B6L)*64+v(B5L)*32+v(B4L)*16+v(B3L)*8+v(B2L)*4+v(B1L)*2+v(B0L)*1+1/256)'

- .ENDS

- .subckt Bitlogictrip BX BXL

- Vone one 0 DC 1.0

- Xa2 one BXL BX trip SW

- .ENDS

- ******会不会是下面这个模块不合适?**********.SUBCKT SW 1 2 3 4Gswitch 1 2 VCR PWL (1)3 4 0V,10G 200pV ,1E-5

- R1 2 0 10G

- .ENDS

- ***main body*********

- VDD VDD 0 DC 1.0

- R2 VDD 0 10G

- VREFP VREFP 0 DC 1.0

- VREFM VREFM 0 DC 0.0

- VTRIP TRIP 0 DC 0.0

- VB7 B7 0 DC 0 pulse(1.0 0 0 200p 200p 1279.8n 2560n)

- VB6 B6 0 DC 0 pulse(1.0 0 0 200p 200p 639.8n 1280n)

- VB5 B5 0 DC 0 pulse(1.0 0 0 200p 200p 319.8n 640n)

- VB4 B4 0 DC 0 pulse(1.0 0 0 200p 200p 159.8n 320n)

- VB3 B3 0 DC 0 pulse(1.0 0 0 200p 200p 79.8n 160n)

- VB2 B2 0 DC 0 pulse(1.0 0 0 200p 200p 39.8n 80n)

- VB1 B1 0 DC 0 pulse(1.0 0 0 200p 200p 19.8n 40n)

- VB0 B0 0 DC 0 pulse(1.0 0 0 200p 200p 9.8n 20n)

- Xa1VDD VREFP VREFM trip Vout B7 B6 B5 B4 B3 B2 B1 B0 DAC8bit

- R1 VOUT 0 10G

- .OPTION LIST NODE POST

- .OP

- .option runlvl=0

- .TRAN 200p 2.6u

- .PRINT DCv(Vout)

- .END

期待大家的帮助,谢谢!

越高位变化时,毛刺越明显

修改后:

.SUBCKT SW 1 2 3 4Gswitch 1 2 VCR PWL (1)3 4 0V,10G 200pV ,1E-5

R1 2 0 1E-4

.ENDS

波形没有明显变化

mmmmmmmm

Set runlvl=6 to get the most accuracy but at the cost of reduced simulation speed!