请教一下,ADC采样保持电路瞬态波形不理想的原因。

时间:10-02

整理:3721RD

点击:

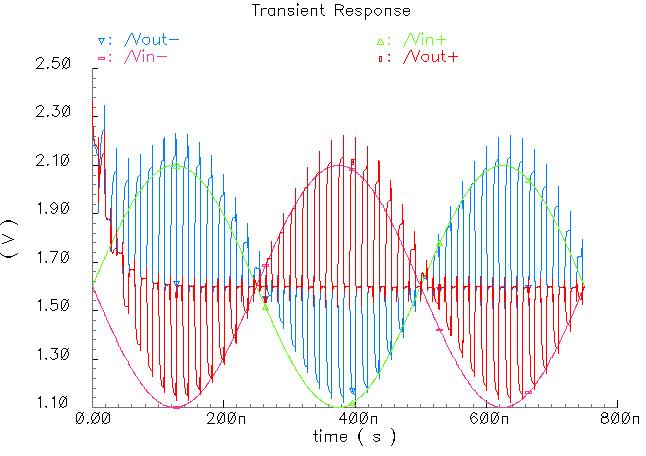

这是我的采样保持电路瞬态波形,十分的不理想

我采用的是电荷分配式的SH电路,共模电压是1.6V

首先,在输入信号上升的阶段,采样保持完成的还算可以,但是在信号下降阶段,保持信号发生了很大的延迟

其次,而且在采样完成后,保持输出的信号顶部都不是平坦的,不能保证稳定的保持输出

最后,上半段的信号,毛刺现象非常严重,而下半段却没有

请前辈高手,略微指点,小弟不胜感激

我曾经遇到过你的第二个问题, 就是采样完成后,保持输出的信号顶部都不是平坦的, 不过我是用HSPICE仿的, 解决方法是在option里面选择optiondvdt=2, 原因请查看HSPICE的帮助文档, 这个可能是软件算法的问题, 加上这个option后可以使仿真更为精确

我也在做s/h circuit,as i know,it's better for you to use the flip-around architecture for the high speed circuit.and from you data,i think the setting time is limited ,so that i can't push the voltage to the desired voltage level during the sampling phase.

我也想问一下,就是我做采样保持的时候采样时钟达不到输入的峰值,也即采样的峰峰值会低于输入的电压峰峰值在双端输入2v时,采样的峰峰值才1.91左右,该怎样解决,烦各位大侠指点指点

第一个问题应该是时钟馈通效应和沟道电荷注入效应引入的误差,应该调整好采样开关的尺寸。

第二个问题应该是采样开关的寄生电容导致的,应该调整好采样开关的尺寸。

第三个问题中毛刺很大是由于时钟导致的,时钟翻转太快以及采样开关的寄生电容都会导致毛刺过大,解决方法:1、增大时钟上升和下降时间;2、在输出端加一个小电容。