一个给模拟和数字部分同是供电的LDO的疑问

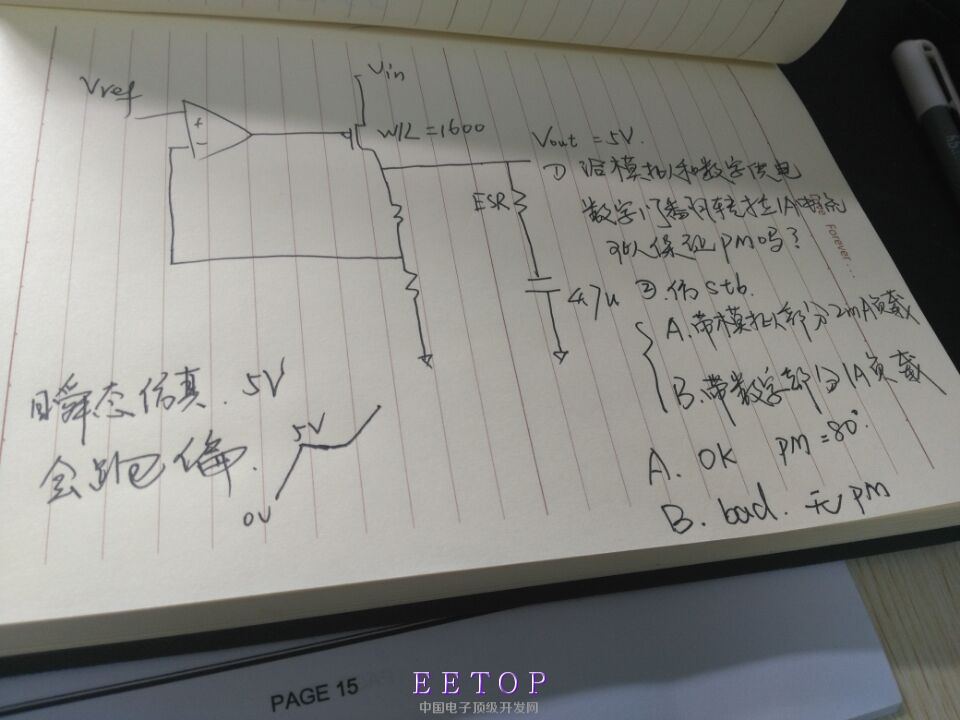

问题在上面图片中提到。

这个是反向的DC-DC中的LDO。采用ESR零点补偿,电容是钽电容。

LDO :VIN:6-30v;VOUT=5V。按照说明书上所说,最大带负载电流为RMS 50MA。

现在我全仿DC-DC。发现VOUT端在数字们翻转的时候输出一个1A的大电流,持续时间5ns,DC-DC周期是2us。给模拟部分供电2MA。

现在我单仿最大带1A负载,发现增益曲线已经变成负的。

疑问1:LDO是不是需要验证1A负载的PM。

由于使用了高压工艺,发现每个管子的ron超级大,gds=10n左右。从而使LDO得EA的输出极点很小。这里EA后端已经接入buffer。

本来我是将输出极点作为主极点:因为输出带4.7uf大电容。这下EA输出端作为主极点。主极点很小,从而使得GBP小。查了下资料钽电容的ESR大概

在20m-50m,取最大补偿。补偿的零点已经在带宽外面了。补偿于事无补。如果ESR再取大,是可以补回来,可是VOUT在拉电流的时候下陷的电压就很大了。

疑问2:问下你们是怎么做LDO同是给数字和模拟供电的高压LDO。

仿真图?。

疑问1是不需要的,瞬态的大电流由大电容放电提供。未完待有空补充

感觉DC-DC里面的LDO不会带1A这么大的电流,是不是哪里短路了。纯属猜测

建议吧数字供电和模拟供电分开,做个双路的LDO。

数字LDO没有必要验证1A的PM,跑一下load regulation,负载1A 5ns。

另外数字电路看一下怎么会有1A的大电流,虽然是瞬时,看看问题出在哪里。

标题

大电流是有电容补给,由于有esr,vout下降,环路反应给输出电容充电。这里有环路调节过程,为什么不验证PM?

标题

因为要驱动一个宽长比1640000/1.5u的功率管。

如果可以的话,延长功率管驱动的非交叠时间。

标题

谢谢指点。

赞同3楼,数字电路的大的瞬态电流造成的电压波动理论上由输出大电容供电,由两部分,一个是△I*△T/COUT,另一部分是esr*△I,这两部分在5nA的短暂瞬态大电流下影响由COUT改善,这也是输出大电容可以改善负载瞬态的原因吧,LDO的环路没有那么大的带宽,如果这个大电流持续时间较长的话,功率管肯定在线性区,失去调整性能,输出电压会下降,且输出大电容的LDO在重载时最容易不稳定。功率管的尺寸应该由平均负载电流来计算吧?期待大神的回复

1. 用ipwl的器件做负载,可以按照你想要的电流波形大致做出个理想负载。仿下TRAN看下输出会不会震荡

2. 500kHz的频率,只有5个ns有1A的电流。你直接用1A做负载,明显不合理。4.7u的负载电容,你可以算算1A*5ns会导致多大的压降

3. 请把1A负载的波特图plot出来。

标题

1.粗略用lpwl仿真不会震荡。

2.变化大概在1.06mv

3.带1A负载,输出电压已经挂了。bode图没意义。

粗略估算输出50mA时片外的零极点的位置基本都是固定的,即使加了30V的电源,情况也没有那么糟糕。内部加了buffer后,按环路增益60dB估算的话,带宽也不是很差,大概100KHz吧。5ns时间1A的负载,没有什么LDO能反应过来的,主要还是靠片外的大电容,而且你后来也计算了此种情况下压降也是几mV级别的,又有什么好担心的呢?直观理解的话,电容瞬态快速响应大电流,LDO环路几十mA的小电流慢充,完全可以的,根本不需要LDO去响应那么大那么快的瞬态电流。

标题

多谢,大概明白了。