这个用在cascode电流镜中的管子是native管吗?谢谢!

native的掺杂不一样,应该颜色不同吧,应该不是,而且电流镜用native没什么好处很亏

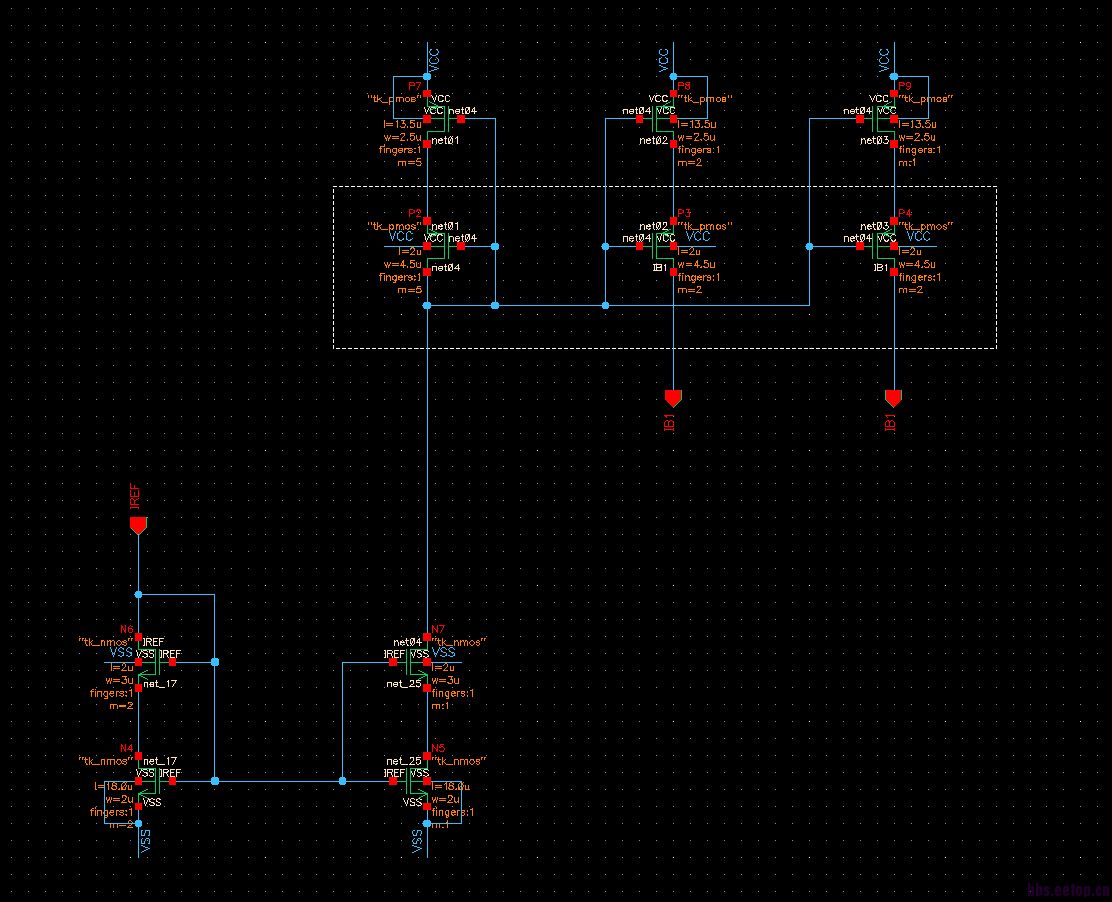

你说的“上面”“下面”是cascode pmos中的上面和下面么?

芯片拍到poly层已经可以看清楚nwell和区分出NMOS和PMOS,所以没拍衬底。

5V的双阱标准CMOS工艺,里面的self-cascode的PMOS和NMOS电流镜全部都是这种类似的管子。

我是这样考虑的

普通的self-cascode输出管要占一个VGS,靠近电源的那个管子处于饱和的临界状态,所以self-cascode的输出电阻和匹配精度不如cascode。

如果这个是native管,假设阈值电压为0,那么靠近电源的那个普通管的VDS增加了一个VTH(0.7V), 处在强饱和状态,匹配精度和输出电阻接近cascode

是指第一张图片版图里面的管子

好多做反向的啊,锅内做正向设计的多不多? 请知道的网友给个大概数据。

native带来唯一的好处就是电压裕度吧,让你觉得vov大一些匹配好点,其实由于是他vth的偏差带来的匹配误差要严重的多,还有噪声大,为了让掺杂的地方不影响其他管子还要浪费很多面积,如果你电流镜对匹配要求不高到无所谓,但要求不高又干嘛用cascode,所以我认为不会是native

另外drain加宽只能认为是加电阻,而且离沟道远了压抗高点,是不是你这电流镜输出接pin的?所以为了esd把drain拉长点。

有道理,不过如果是普通管的话,两个管子的W/L比差不多,作为self-cascode的使用尺寸不合理,靠近电源的管子进入线性区了。

都是内部小电流(uA)电路,没直接连PAD。

下面是对应的NMOS cascode管layout

再下面这张图是以前反向的耗尽NMOS管,layout和上面的NMOS很相似

所以现在比较倾向于耗尽管,不过看来这种结构除了输出电阻大没什么好处

selfcascode本来就是让靠近电源地的管子可以到线性区来应对低电压,所以我觉得尺寸到不是问题,看上去觉得是合适的。但我看到n管的两个上面的管子单独和下面的隔开了,那我想你说是native可能是对的,再看p管也是隔开了,恐怕是用于特别低压的情况?

多谢帮忙分析!,这个芯片的工作电压2.3-6V,是普通的工作电压范围

小编,看看这个帖子。猜测你这是一个电源芯片,这种电流源结构在低电源电压的时候效果不错。

http://bbs.eetop.cn/thread-99306-1-1.html

这是MPS的电源芯片吧 5V 以及这种结构 都符合他们的工艺和风格