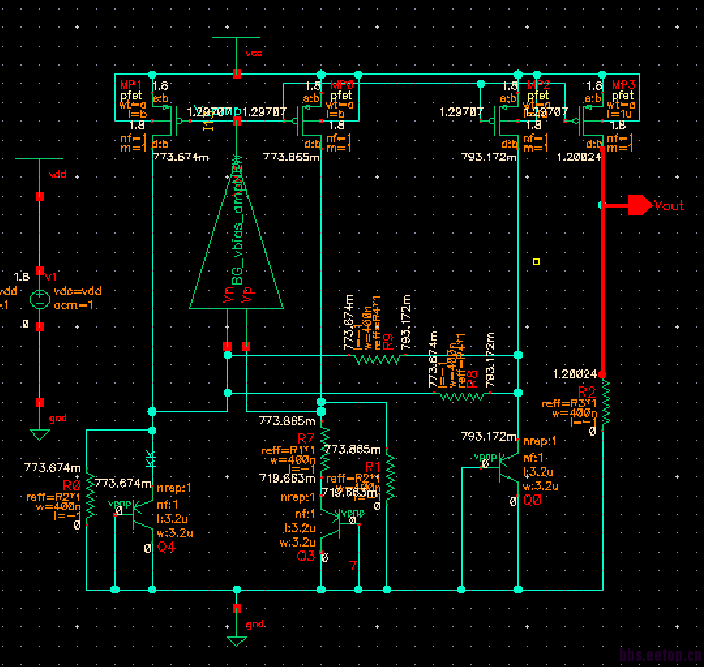

电流求和带隙基准PSRR怎么提高

菜鸟一枚,向各位大神求教求教~

估计偏置点都不对了吧,加cap

你的三极管个数都是1吗?

R8,R9怎么都接到Vn了

三极管个数是171

R8R9是为了二阶温度补偿才加的~

MOS管都工作在饱和区啊,这个没问题~

你说的是DC PSRR吗?请问电源电压多少?如果是DC PSRR,应该设计有问题,仿真PSRR多少? 我认为在测试时你的 BG 好像就没工作。

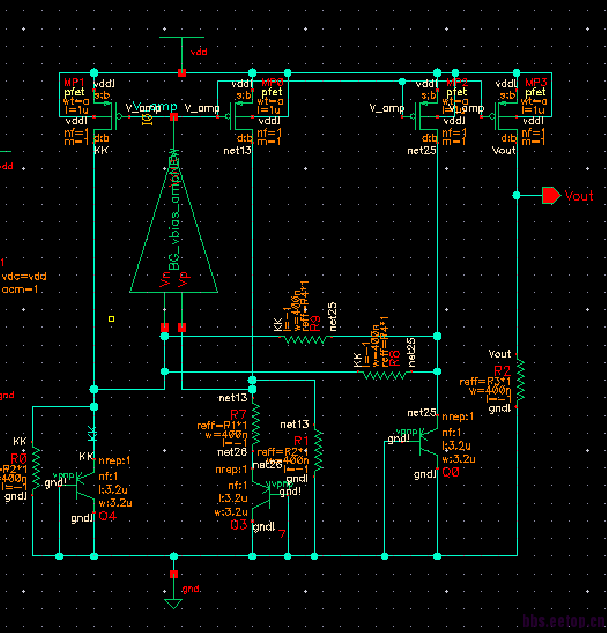

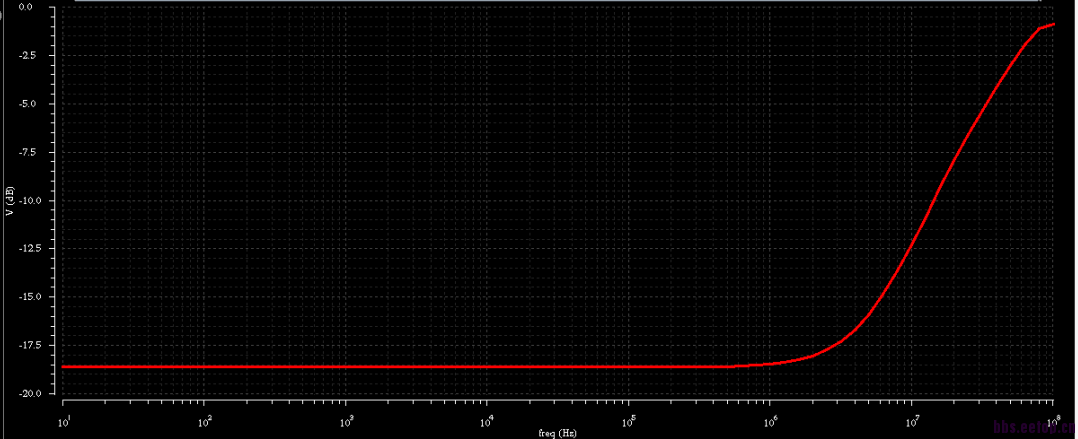

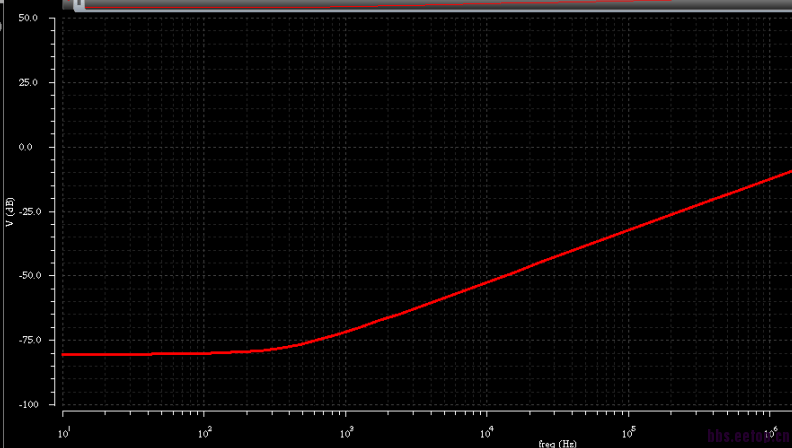

我的电源电压是1.8V带隙输出电压是1.2V我测量PSRR就是在电源电压vdd上加了一个小信号量acm为1v在带隙输出端交流仿真测出PSRR. 大约为18DB

二阶温度补偿是这么接的么?

提高电流镜阻抗,电源对输出的影响就是输出的电流镜阻抗和电阻的分压关系,现在你DC的psR都这么低,还不到加电容的时候,先提高电流镜的L再说

cascade

谢谢您的指点!明天我试试看! 可能是这个工艺的问题,现在用的折叠栅放大器增益就只有60DB.,也是PSRR这么低的原因,但才18DB低的有点离谱啊。我想用二级的放大器,又怕相位裕度太低,稳定性不够。苦恼ing...

你 运放电路什么样子的? 运放的PSRR多少? 管子PM0/1/2/3是否在饱和区呢,L可以加大点试试。

你是测试还是仿真?

vout在环路外面,你调节运放增益效果不大,还是从电流源着手

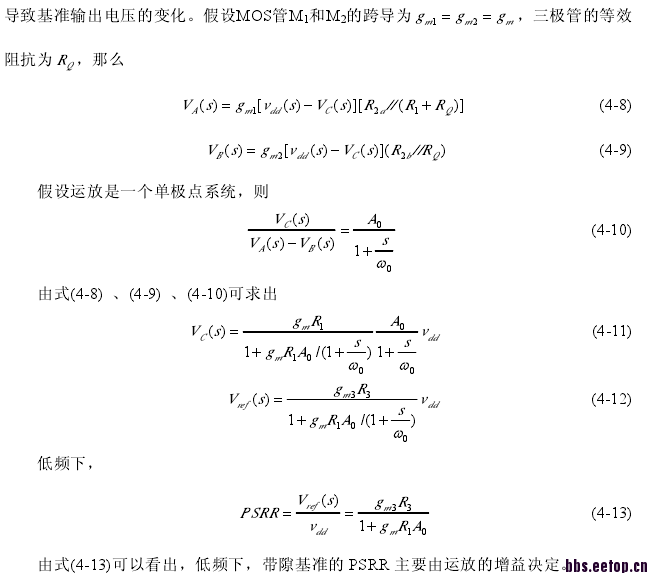

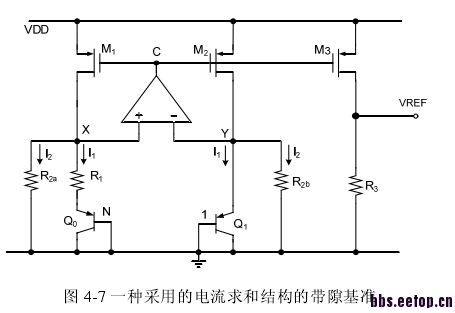

感谢您对我的帮助!我真的很需要~ 我在一篇文章里看到和我用一样电流求和模型的带隙基准结构,文章中对于带隙PSRR的计算公式如图所示,图中计算结果表明低频下,带隙基准的PSRR主要由运放增益决定。他采用的结构和我的一样,似乎运放增益是PSRR很重要的因素。您帮我看看呗~ 谢谢啦,感激不尽!(他推导中的A、B点应该是电路图中的X、Y点)论文是:基于40nm工艺的CMOS带隙基准源研究与设计

这是仿真结果对吧。我认为不是调什么参数能解决的,感觉是电路没有正常工作,即使你的电流源L 很小PSR也不止这些。建议在AC仿真时,看看DC,你可以贴张DC point 的图吗?

1.8V电压,输出1.2V,不建议用current model 结构。这种是用在低电压情况下。

PSSR 方针结果好象不正确。

一般是高pssr @ low freq, 然后 roll-off as freq increases...

肯定是simulation setup搞错了。这个结构不可能只有18db pssr. 在地频率至少了会有40-50 db, typical case.

你的电源1.8v,输出1.2伏,其实可以cascode结构来增加pssr. 但有可能在corner的时候不工作.

工作点都是没问题的,管子都能工作在饱和区。

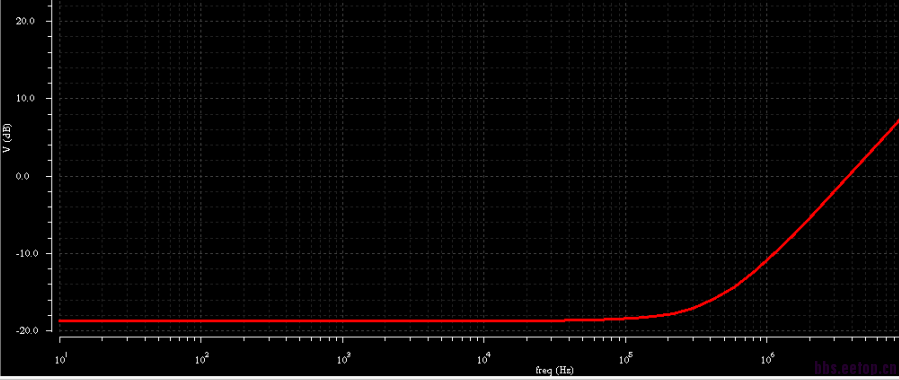

我也很奇怪为什么PSRR这么低,我的PSRR仿真时就是在电源电压下加一个acm为1V的小信号,交流仿真输出点Vout的AC特性。然后我把放大器改成了二级的结构,增益大概80多DB,放大器的PSRR也能达到80DB。把这个放大器用于带隙中,我设置了两个电源:一个VDD给放大器供电;一个VSS给带隙电路除了放大器部分供电。分别对两个电源VDD、VSS加小信号,仿真PSRR。发现放大器电源电压VDD有扰动时PSRR能达到75dB,其他电路的供电电压VSS有扰动时PSRR只有不到20dB。也就是我的带隙基准的PSRR小和放大器的增益关系不大,主要是外部电路的问题,我按上面几位吧友说的增加了带隙管子的L,PSRR改变的也不是很明显。好苦恼。

大神你说的还真对。我今天把运放改成2级的,增益85DB,结果PSRR还是没什么变化,就是外围电路的问题。但我按您说的增大了那几个管子的L,PSRR有一点上升,但是还是才到20DB。增大管子的L时是不是W也增大,保证W/L不变的啊?我是这么增大L的。问题还是没有解决。向大神求助。 期待您的回复

把电源电压设为1.6V,看看输出还是1.2V吧。建议把Opamp里的电源做为PIN引出来。

show your amplifier

等等,你怎么有两个电源?看PSRR你该把运放和BG电源接一起看

我在上面24楼解释了为啥两个电源,你看看~~

把输出级的电流降一下会有效果吗?