noise aware PLL flow 的参数设置问题

时间:10-02

整理:3721RD

点击:

我已经提取了PFD+CP的macro model以及VCO的PPV model,在pll-bench仿真的时候,会出现环路无法锁定的问题。在transistor level的仿真中,环路在30us左右就锁定了,但是在使用noise aware PLL flow仿真的时候,在本应锁定的时刻,会出现Vtune在对应电压值周围波动的现象,且幅度较大(约200mV),并且该信号具有一定的周期性。通过这种仿真得到的phase jitter比预想值要高两个数量级。

现在不太确定原因出在哪里。大概想了想,可能有以下几个问题。

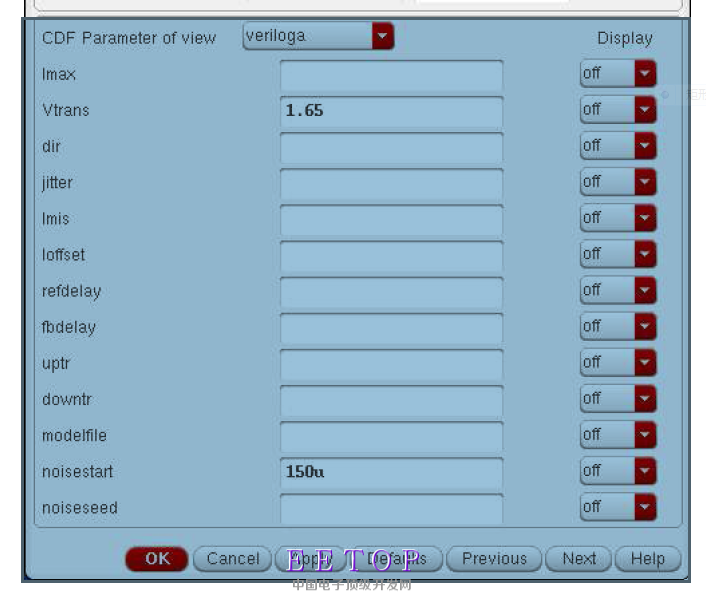

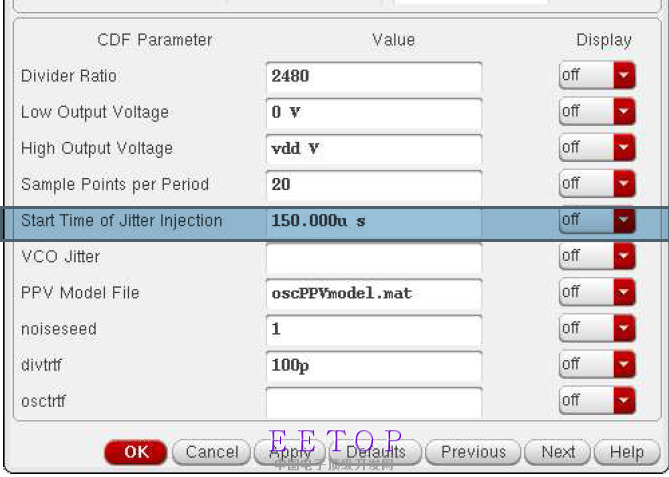

1. PFD+CP的model中某些参数设置不合理。各位曾经跑过这个流程的,能否说明以下各个参数都是如何设置的?

2.在PFD+CP的model里以及VOC的model里,还有freq_meter这几个模型,都有一个跟噪声模型注入有关的时间,这两个时间又该如何设置?还有前面那张图上的noisestart. 跟锁定时间有什么关系?

还请各位了解的大神不吝赐教。O(∩_∩)O谢谢!

现在不太确定原因出在哪里。大概想了想,可能有以下几个问题。

1. PFD+CP的model中某些参数设置不合理。各位曾经跑过这个流程的,能否说明以下各个参数都是如何设置的?

2.在PFD+CP的model里以及VOC的model里,还有freq_meter这几个模型,都有一个跟噪声模型注入有关的时间,这两个时间又该如何设置?还有前面那张图上的noisestart. 跟锁定时间有什么关系?

还请各位了解的大神不吝赐教。O(∩_∩)O谢谢!

大概找到问题了。在提取PFD 模型的时候,Load的电压值没有设置为环路锁定是的电压。还有就是电路里有一个bias电路,在设置pss的tstab时, 没有考虑这个变身电路的启动时间。

问下小编整个流程跑通了么? psd plot的window size你给的多少啊. 我尝试过1024 4096 8192...等等不同的值,对reference spur的值有一定影响,应该怎么设置呢