PLL无法锁定

我设计了一个8GHz 小数电荷泵PLL,fref=20MHz,Kvco=100MHz/V。为适应小数工作,用的3阶无源LPF,fc=200KHz。使用candence spectreverilog进行前仿真,小数部分用verilog生成funtional。目前先没有接入SDM,只带着PScounter进行N=400的整数环路仿真. 调谐曲线趋向稳定后又出现了波动,幅度大概30mv(375ppm),应该是没有锁定。

期待各位大牛给予指导,多谢!

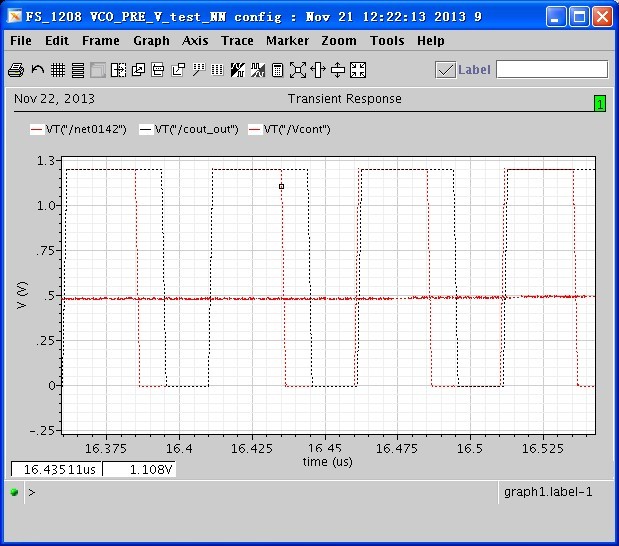

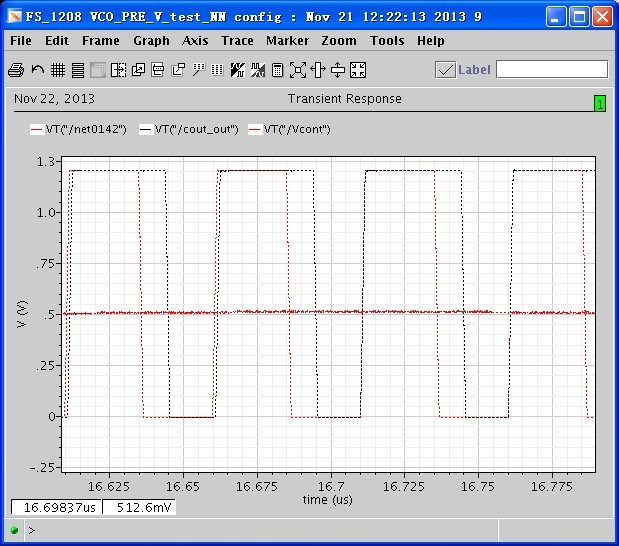

后续问题:感谢各位大牛给予的指导,我把仿真精度设置为moderate 10ps,但是得到的控制电压依然存在之前的现象。附上抖动发生时PFD的两路输入,在峰值发生前后同频同相,没有相位差,应为mismatch的存在导致环路不能真正锁定,所以产生抖动。请问这种情况是什么原因呢?两路信号一路是vpluse产生的20M参考电平,一路是verilog数字模块输出的数字电平。谢谢各位!

Is your simulation time long enough ?

How about your R1 and C1 ?phase margin ?

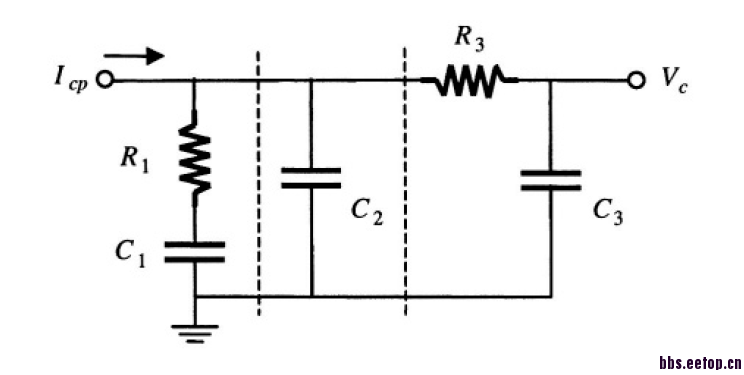

仿真锁定时间是4/fc=20us粗略估计的,不过现在仿真到33us情况还是这样。R1=11.9K,C1=280p,C2=19p,R3=23.8K,C3=1p, 设计相位裕度在56°,Icp=400u。仿真精度设置是moderate 5ns,会不会是仿真精度不够呢,谢谢!

控制电压

LPF

看样子是系统级的问题,你的ref只有200Mhz,你的bandwidth多少,我估计<1MHz比较好。

你的RC参数和Icp设置。

8Ghz的频率太高,divider会不会fail?

参考频率是20M,带宽是200KHz,三阶LPF中,R1=11.9K,C1=280p,C2=19p,R3=23.8K,C3=1p,Icp=400u,设计相位裕度是56°。仿真精度设置是moderate 5ns,是否可能是仿真精度不够的影响,谢谢!

参考频率是20MHz,带宽200KHz,R1=11.9K,C1=280p,Icp=400u。分频器前仿功能正常,应该不是这个的问题

20Mhz

上面说错了。

仿真时间是根据4/fc=20u估计的,目前到35us情况仍然存在。 R1=11.9K,C1=280p,Icp=400u,裕度设计为56°

我的仿真精度是moderate 5ns,是否可能是仿真精度不够导致的,谢谢

根据你波形17us-20us的纹波来看你的带宽比200KHz大很多。从15.5us--19.5us,你一个出现5个纹波基本上是说你的带宽大约1MHz--1.25Mhz。

可以贴出up/dn的信号吗,这个更加容易看出来

c2 多大?

我计算了一下,根据你给我的值你的带宽应在1.2Mhz左右。

M=400

damping好像不够。只用大约0.4-0.5

这问题太简单了:仿真精度不够。请提高仿真精度

这个震荡我觉得是一个自主的调节了,应该不是LPF能滤掉的。带宽粗略根据fc=Icp*R1*Kvco/2*pi*N=198KHz。up/dn信号有的,我应该贴哪一段的图呢?

你算出来的是1.2M rad/s

人家算的200KHz没有问题

C2=19p, R3=23.8K,C3=1p

我用的是razavi书上P468的公式,你说的这个少算了一个2pi。

100MHz/v 换成 628Mrad/V.

你再算一下damping。

贴图就贴震荡部分的。把vctr也放在同一张图。

谢谢回复!确实也有朋友说是仿真精度不够,我不是很理解精度为何使控制电压出现这样的现象,一直以为精度只是促使振荡器起振用的。

观察一下VCO的频率是多少。

sorry, 我的带宽算错

那如果damping也没有问题的话,就不是啊环路稳定性的问题。

想回复你可是一直显示管理员要审核帖子。damping和相位裕度有关,这个环的裕度估算是50°~60°。

管理员是不是觉得我们在灌水,

如果是你的KV只有100Mhz、V,所以应该用了multiply VCO curve.会不会在换VCO

曲线的时候出现不连续从而导致不锁定的。

我今天回复帖子一直这样,不清楚为何。确实用了4bit的电容阵列,然后选中其中一条curve达到目标频率,没有进行bit的切换。我恢复了10ps的精度在进行仿真,不知道能否解决这个问题。

这是出现波动时的up/dn信号,我观察PFD的输入,直观上看波动的产生是因为两路输入的相位完全一致了,理论上应该会有一个小的相位差来抵消CP的mismatch,于是环路又重新调整,以此反复。

up/dn

晕,分成3栏,要不什么也看不到。

the simulation accuracy should be at least 1/3 smaller than the VCO highest period , please use the default simulation accuracy in moderate mode.

现在已经设置为1/10的周期在仿真,思考了下,是不是因为PFD比较两个信号时在采样点上的差别,导致了控制电压的不同?