LDO上电过程的波形求解

时间:10-02

整理:3721RD

点击:

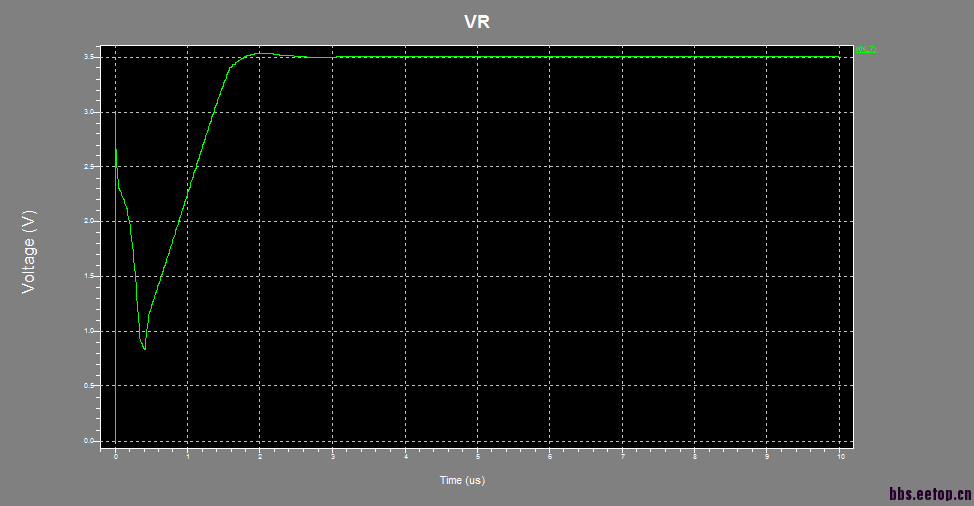

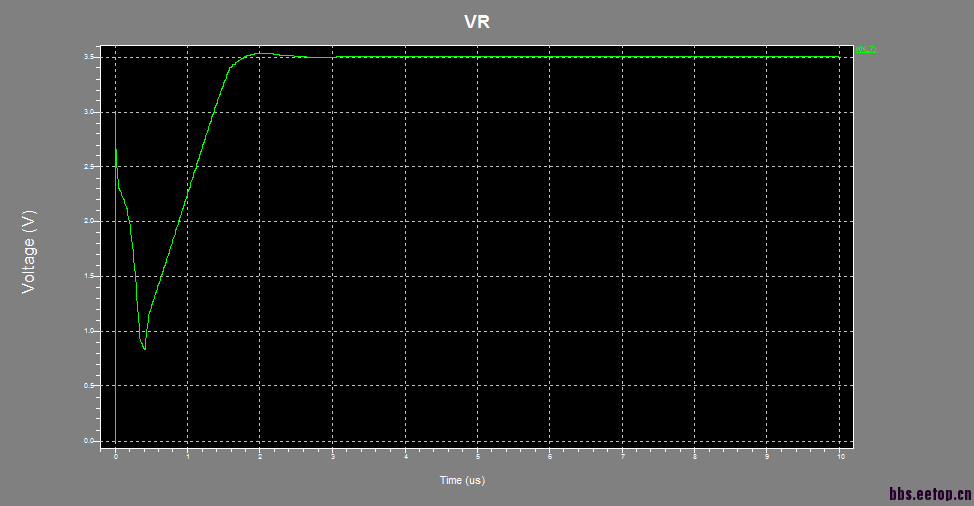

在下刚刚开始接触LDO,刚刚做了一个练习。在瞬态仿真上电过程的时候看到这样的波形:在上升到设定的电压之前有一个很明显的下滑。在此请教各位前辈指点一下,这是什么原因造成的?对LDO有何影响?

先在此谢过!

先在此谢过!

查看电源上电时间,pmos栅极电压,bgr电压

上电太快,输出couple到反馈电压,造成LDO回调。

谢谢,我再研究研究。

上电时间设计的是1ns,请问根据您的经验,设定多少合适?

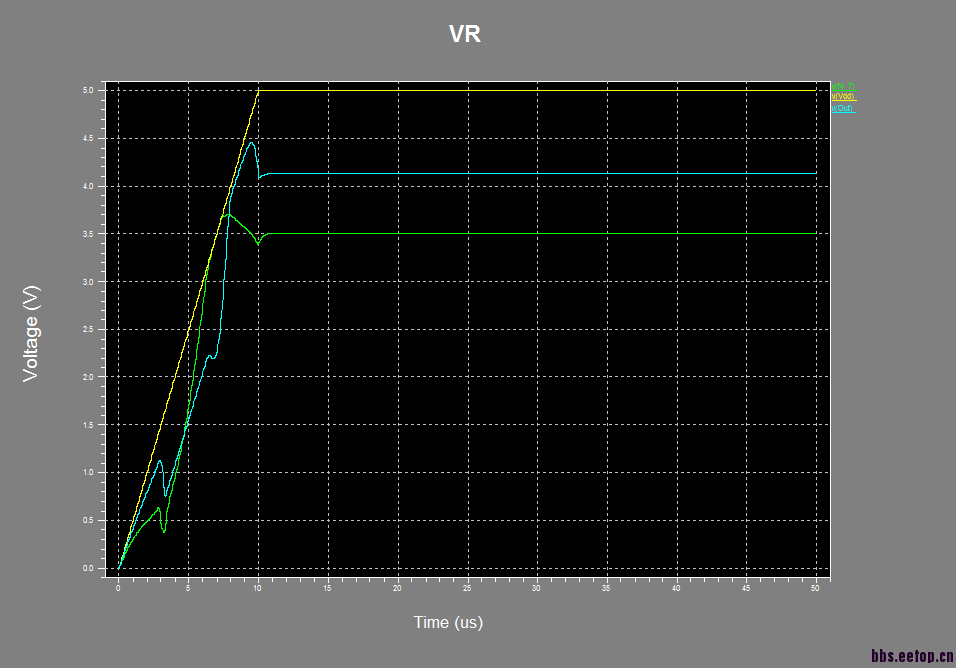

您好,这个波形是我把上电时间设定为1s时的输出显示,黄色为电源,蓝色为PMOS栅极电压,绿色为输出电压。把上电时间延长以后所出现的跳动没有那么明显。还麻烦您指点一下这种现象出现可能的原因和所造成的影响。谢谢!

LDO设置enable信号和软启动控制,你看下你上电过程中输出管输出电流的波形。

多谢指点,这个现象应该是EA内部的问题,我试了下EA单独上电也会出现这个过程,可能是因为采用特殊工艺的缘故。非常感谢。

你好,我现在也碰到这个问题,最后也发现是在EA带来上电的过冲,请问你的最后解决掉了吗?

我现在也碰到这个问题,也没有解决,原因不清楚

check the start-up circuit!

没有软启动电路么?

确定上电斜率,加软启动电路。一般都是EA输出导致的这个现象。

学习了

EA的反應時間, 加個soft-start看看

看一看,学一学。

PASS管用N的吧。除了这个 不治病。

老了。