求教如何减小电源和地的抖动

没电容高频charge 谁提供?

是什么电路? 环形震荡还是buffer 整形?

Use very wide power & ground metal line (top metal is better, or parallel top metal with other layer metal) direct feed power current from power & ground PAD, you can use large decopling cap. near your osc circuit. If floor plan is possible, place your circuit near power & ground PAD. Your power & ground pin outside IC should decoupling with 0.1uF cap. parallel with 1uF+ cap. 0.1uF cap on PCB shoule be very cloce to IC pin. Or you can use double bound of VDD & GND. Do you simulate the bounding wire effect?

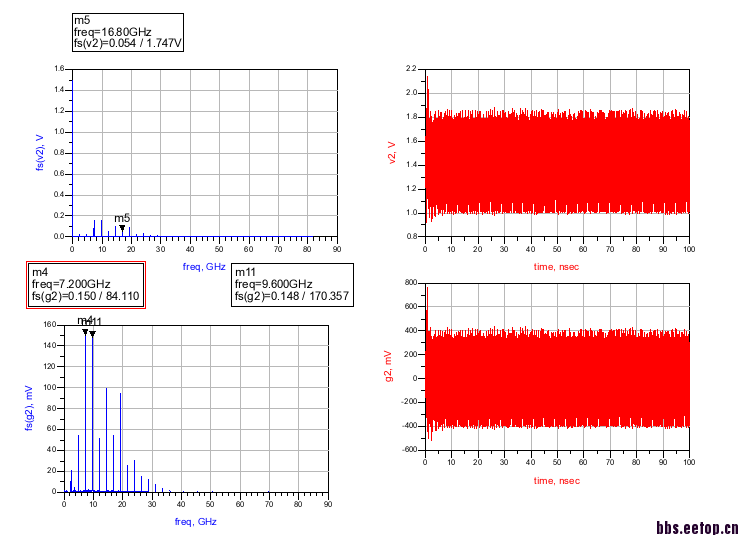

could you post the simulation voltage & current waveform of the power & ground ?

谢了,的确是电源线很窄,压降有点大,我用了宽的电源线,用ADS看了下,电源端的频谱,噪声还是很大,我是用反相器驱动后面的mos管

Do you use inverter output as the power to feed the other circuit block?

If the answar is yes. Please enlarge your inverter PMOS size (enlarge W, minimum size L), NMOS is no matter (it is off in your case), then put a capacitor (top plate connect to inverter output, buttom connect to GND, keep metal wider) after the inverter, the capacitor (MIM, PIP or MOS cap. MIM is beter, try 10pF level) should be placed near the post circuit. Maybe you can series a small R (10~100 ohm) after inverter, before capacitor.

Check the waveform of the inverter input, if it is also noisely. Put a capacitor with top plate connect to the inv`s input and enlarge it`s driver. The driver`s GND (wider is better) line should direct connect to clean GND PAD or GND PAD. VDD should direct connect toVDD PAD with another line (wider is better).

Analog block should use higher voltage, try to suggest your boss use larger VDD.

From your waveform your inverter`s input is also noisely. It is coupled from inv`s output by parasitic cap. & power rail (GND).

我是输入横幅的正弦波信号,输出方波信号控制mos管,是做功放电路,总共分成19个控制端,你的意思是在每个控制端反相器后面都并联一个电容到地吗?那会不会太多啦,每个反相器接的是的是160u宽的管子的栅极,反相器nmos尺寸已经有20多u了,很大了

You can use smaller NMOS in the inv. since it is no use in your case. Maybe w=2u.

Since your PMOS`s Vgs always transition,then PMOS`s rds is not constant, if you make PMOS`s behavior like a constant R maybe the effect will decrease.

Try to put capacitor before the inv`s input maybe 10 times larger of (PMOS`s Cgtot) between inv`s PMOS`s gate & source (Make PMOS`s Vgs as constant, then rds is constant). Every inv`sPMOS use how well (NO body effect). Let every PMOS`s Vsb = 0, seperate every inv PMOS`s NWELL. use very weak driver (small W, large L) to drive the inv, maybe you can series a large resistor (or NMOS with large L & small W) to lower the transition effect from driver.

Maybe you can use a small boost circuit to increase the PMOS`s NWELL voltage when it is turn on, then you can make your PMOS`s size smaller.

你可以試著在PMOS上加固定電壓源(Vgs=VDD) 看還會不會有這一現象 如果沒有這個方式就可以解

想了一下 你的power down控制法有點怪 其實只要把每一個電路block powerdown 掉就好了 不需要在power line上裝那麼多個switch 會有一堆LRC寄生問題 會產生震盪是必然的 把電路powerdown 其實很簡單把bias關掉 NMOS gate 接地 PMOS gate 接VDD 就好了 課本上都有電路

其实你的问题大概需要两方面想办法,一边是减小电路供电节点的对地(系统的地)阻抗--加宽金属连线宽度和/或加大decap电容等等,另一方面是改进电路设计减小瞬态电流最大值,或者叫电流spike--减小撬杠电流等等。本质上讲,就是个分压关系,供电节点到地的其它部分形成的阻抗(包括电源连线所有LCR,甚至电源内阻也需要包括在内)相对电路工作时阻抗及其变化,如果供电点本省阻抗够小-->远小于电路操作时阻抗,那就没有道理会看到供电节点严重“bounce”。所有正确的有帮助的办法一定可以归入其中,不能在此两方面或其一有所帮助的,基本可以断定就是在把问题复杂化,是在误导。

如果你真的有本事 不要放馬後炮 不要講一些原則 有本事站出來解掉這一題 (ALL layout by land calculation and tell us why & circuit design for each MOS by hand calculation and tell us why) 沒本事就閉嘴

你這麼厲害 要不要教我們怎麼設計 analog sigma delta ADC modulator(real circuit, 24 bits), how to design coefficient , how ro design each OP, each capacitor , each MOS & layout consideration by hand calculation, how to design 2nd order DEM? how to design multistage decimation filter by Verilog ?

不要拿一些paper出來鬼扯

順便也教大家一下 how to design multi-stage intepolator by Verilog? How to design post analog filter for SDM DAC (real circuit, 24 bits) by hand calculation for each MOS, R, C and why? 還有 Layout consideration by hand calculation? And why?

不要拿一些paper出來鬼扯

要真的會動的東西 有本事站出來 沒本事閉嘴

你真的會設計電路嗎? 有設計過會動而且high performance的 analog IC嗎? 不要光拿paper出來鬼扯 show一下你的本事 拿出你的成果給大家看一下.

看你能提供什么样的平台,能付多少钱了,如果你诚心并且能做得了主的话可能还真有机会。可以认真想想。台湾是不会去的,美国或者大陆都可以考虑。

我自己就會了(analog & digital) 閣下還是另找出路吧

还真没看出来。阁下挺爱学倒是不错,爱学和学明白还是相隔千山万水的。开个玩笑,也不用生气,只是抛砖引玉,还是共勉吧。

如果连原则都不明白,问题怎么会解决明白呢?本人也就只见过模拟电路大海里的一瓢水,不过自认为,那瓢水在我眼里已不再是一瓢雾水,对那瓢水还是可以看到底的,而且从那瓢水里我还看到了天的影子。

大家互相勉勵 為中國的電子科技業共同盡一份心力

小编见笑了。

没事,我菜鸟刚毕业不久。我笑你把人家激怒了。

我太不小心了。不过那位兄弟还是做过不少东西的,论坛还真需要这样的人多一些。

这么高的频率,又是这么大的驱动。所以,在每一级大尺寸的INVERTER状态翻转的时候,都需要从VCC charger电荷或者向GND discharge电荷,尺寸越大,加之驱动速度又很快(2.4GHz)所以每次状态的变化都伴随着大量电荷的瞬间转移。如果你的logic supply是直接来自于一个外部电源或是一个存储了大容量电荷的电容器等等之类的东西,那VCC和GND就不会有大的抖动。还有,虽然你的地和源一直在抖动,但是你看看两者的差值是不是时刻保持一致的,我觉得只要两者的差值都一样的话,那就问题不大。因为本身地和源就是相对的,讲究的是差值而已。防止抖动,最好的方法就是,两条,,,一是试图去想办法增加电源储存的电荷,能够满足logic瞬间翻转所需的电荷,要远远大于所需哦,,,,二是试图去减小logic状态转换时所需要的电荷量,也就是可不可以在满足设计spec的前提下去减小其尺寸。或者,比较先进的一种方法就是,你想想可不可以让VCC的charger电荷和GND的discharge电荷反复利用,,这样既高效,又先进。

在中国的论坛回帖么,最好使用国文。打英文是不是显得自己有多厉害?

加本地电源与地之间decap使本地电源和本地的地同时bounce对于该模块本身工作是影响不大。如果该模块与其它模块所对应地不同时,相互对话还是可能会有问题。如能彻底“消除”bounce应该是最好的解决方案,当然是要有代价的。

我建议他用英文,否则他用繁体字,看得头晕而且很多词别扭比如:类比

我這是繁體字 考慮到有些兄弟會看的頭暈 所以用英文