Bootstrap动态性能问题

我在实作10bits SAR ADC使用90nm,

我的性能一直上不去,所以我来测试一下Bootstrap性能

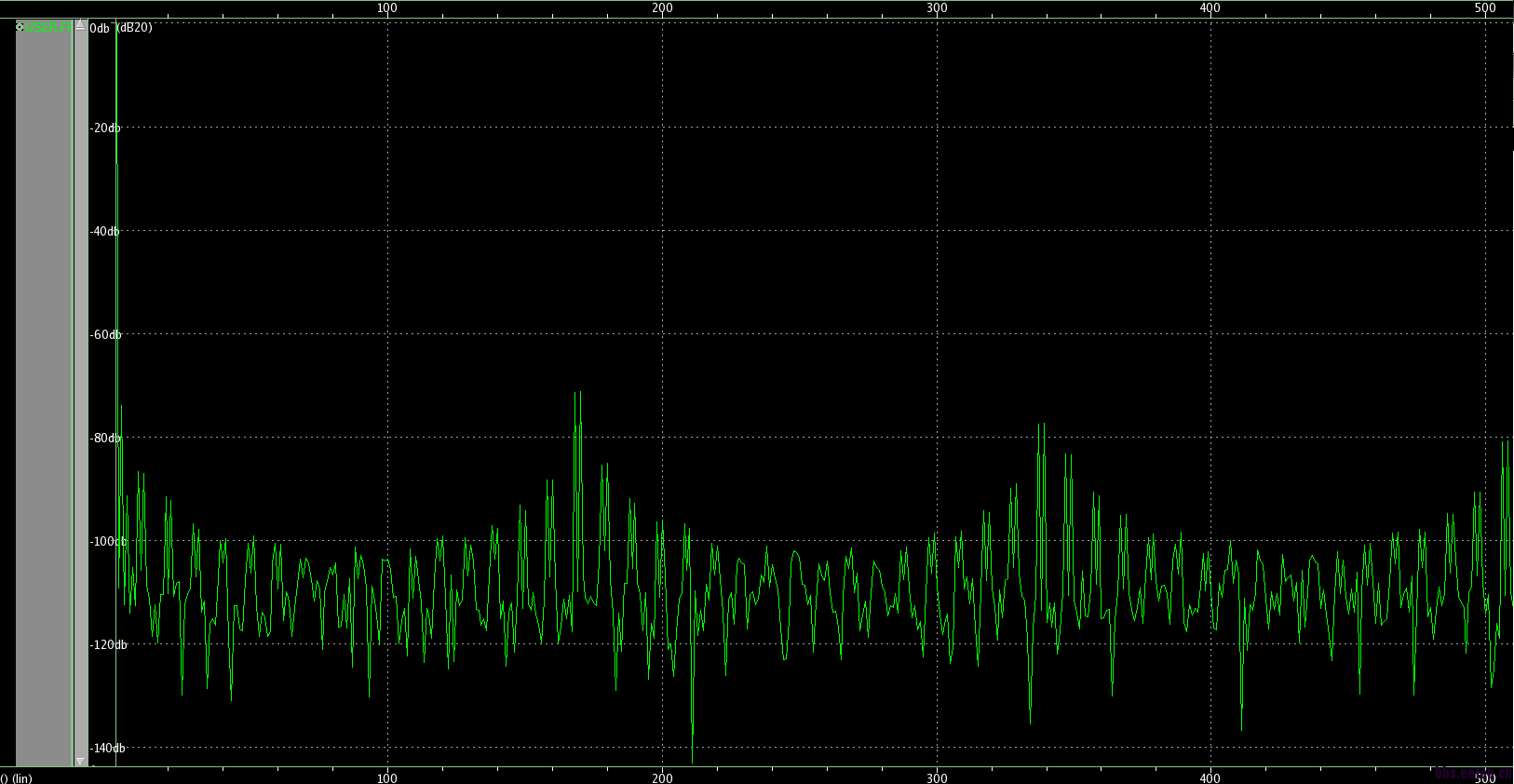

取样率100Mhz 输入频率 1Mhz下 ENOB=13.057SFDR=83.33dB

但是换成 输入频率 10Mhz下 ENOB=10.45SFDR=69.82dB

我之后是要做到400Mhz的取样率,但是连100Mhz都做的不是很好...

这样的Bootstrap是不是会导致我的全电路性能不好?

那应该如何改进?

谢谢各位的帮忙了

我Bootstrap 测试使用1024点的FFT

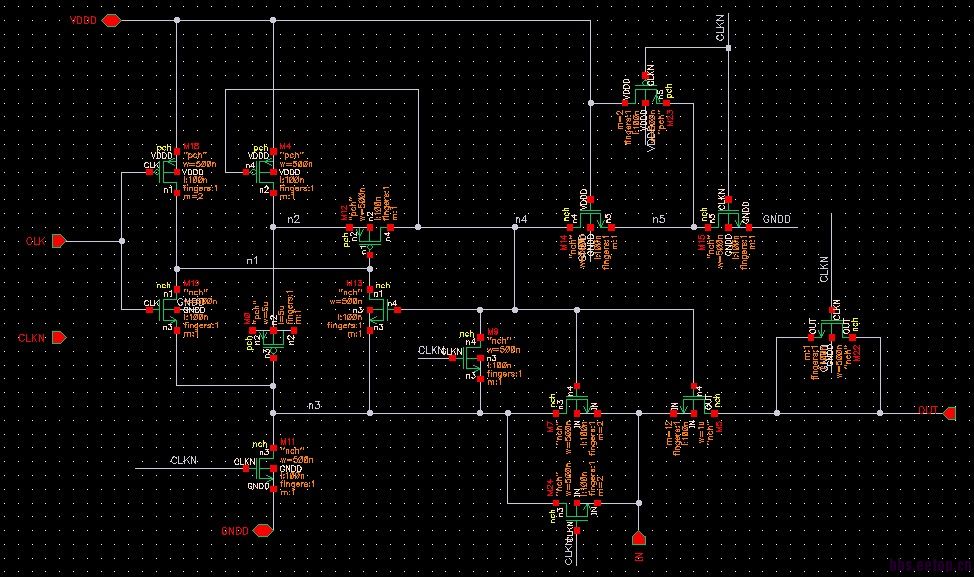

Bootstrap如下图

没人可以回答嘛?

我是参考 2014 IEEE "A high performance Bootstrap Switch for low Voltage Switched-Capacitor Circuits"

自己顶

你的 10bit sar可以达到400M的采样率?是不是有点屌

在IEEE已经有SAR可以做到1G了,所以老板希望速度要好,但现在100M就很难做了...

你确信他们是单通道1GHz10b SAR?

标题

我看到的都是6bit 做到1g的,或者10bit时间交织

把你的时域仿真特性拿出来看看你是测试单路的性能吗?换成差分的试试像电荷注入 时钟馈通这样的共模误差都可以通过差分结构消除大部分

你的开关管做的多大?现在的现象是随着输入信号的上升采样结果THD下降,貌似同你的这个开关管本身阻抗的非线性相关。

谢谢大大们的回应

我之后也是打算作双通道的sar adc

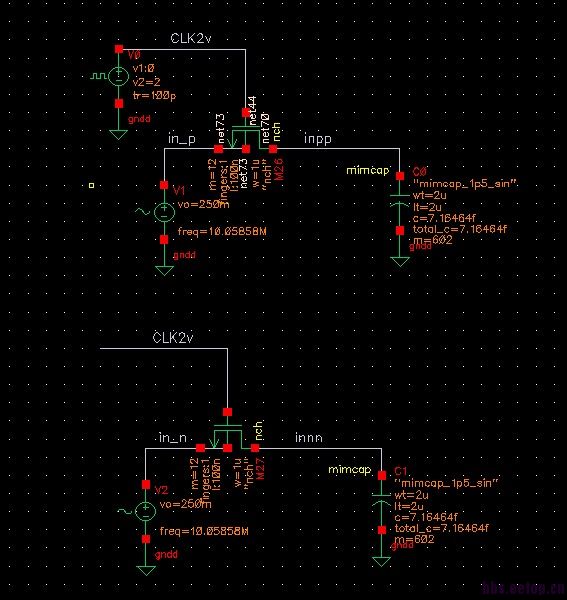

另外下图示我的时域仿真特性图,100M取样率,10M输入 ,希望能请大大发现问题。

xuriver2012大,我的开关W/L = 1u/100n m=12,这样会太大嘛?

再次谢谢各位

继续顶,问题还没解决阿,谢谢各位了

支持你,学习看看

学习看看

感觉你这个做不到这么快的速度啊,10bit做到200M差不多顶天了, IEEE上应该是多通道的吧~

我觉得是你3次和5次谐波太大了,你试试把传输门尺寸调小一点,还有最好做差分电路,总体来说你这个是输入频率增加导致非线性,一般这个都是接近奈奎斯特频率才更明显啊。

你是怎么看出3次和5次谐波很大的?求指教!

谢谢zengyl的建议,我会试试看先打传输门尺寸调小一点,有问题在请教您,

在弱弱的问一下,请问全差分的bootstrap该如何下手?

谢谢了

我看SFDR啊,采样速率提高了,SFDR就下降了这么多。说得不对请指教

有效果了没啊,全差分不是做两个完全对称的就行了?

谢谢各位的建议,但還是作不太出,我在100M的取樣,10M的输入频率下还是答不到ENOB 12,还是只有10左右......快崩溃了阿

小编贴的是时域仿真波形我没看到SFDR在哪啊

看帖子不细心啊。第一楼就贴了

各位先进好:

过了两个星期了,我的电路能就失败....原本想说这个电路最重要的就是那个开关,所以单独的测试一下,

如下图,在输入频率10M下ENOB还是很烂阿.....ENOB=10.715

Gate接时脉为2V以保证导通,输出负载为单位电容7f M=602

输入为0.6V 振幅为0.25的sin

有点混乱,LZ不是在做bootstrap, 怎么又拿个NMOS在simulate? 另外, clock 是2V? NMOS的body接到输入端? channel length =100nm 而不是min channel length?

小编不是搞bootstrap吗怎么又开始测单管开关了?另外,开关管不能把body直接接到source上,这种消除body effect的方法看起来美好,实际上在TH中输出端保持的电压某时刻重新采样后可能会比source低,也就是比body电位低,这会导致drain端的PN结正偏,你的电路就完蛋了

我是想继续测试Bootstrap,想不到方法试了,所以把Bootstrap的开关mos单独测试...,但还是没什么结果...崩溃阿......

bootstrap开关电路,调试的时候主要看你开关在有信号的情况下vgs的保持的多少,是否接近电源电压,

波动有多少,另附开关的source一定要接地,

实际上单个开关应该二阶会大,因为有衬偏效应,这时可以把开关尺寸做大点

另一个做法是仿出开关的阻值大小,算RC频率,看是否比采样频率高4-5倍