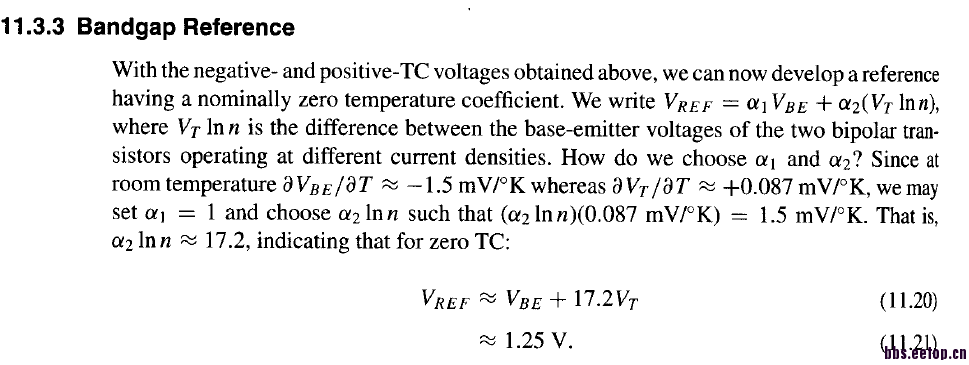

一个关于基准的问题

这个1.25V的基准电压是在300K时推得的,也就是因为要让300K时温度曲线斜率为零,因此得到了一个正温度系数,而恰好这个系数可以让TC=0时输出1.25V的电压。

我的问题是,在300K时得到TC=0,而且恰好输出电压为1.25V不是在任何工艺下都可以实现的吧?

不同工艺,略有却别,但是原理一样的

对,Vbe不一样。有时候BJT的温度变化也略有不同。

就是说我现在在实际的工艺下调基准用拉神的这种PTAT和Vbe叠加是有可能得不到300K下TC=0且输出1.25V的是吧?

不同工艺下面的bjt具有不同的温度系数

对,比如65nm 1.23V,40nm 1.225V, 28nm 1.219V,16nm 1.182V

用16nm的公司还真不多,

OK谢谢

16nm?!只有DRAM,手机芯片和高端仿真开发板采用

28nm做绝大多数产品够用了

1.2 is the magic voltage(band gap) for silicon at absolute zero degree. Non-ideal factors(process spread, op-amp offset, current gain variation, current mirror mismatch etc.) finally make the output have normal distribution.

DRAM工艺和常规IC的工艺基本不是一条线吧。话说TSMC的16nm不是可以用了么已经?

bandgap通过合理的设置,可以得到除了1.2V的其余你想要的电压

是的。、大陆的厂家估计也只有华为的麒麟尝试了16nm,其他的还是在28nm

为什么1.2V得不到?另外,我希望的是在300K时的TC为零,而这个时候恰好输出也在1.25V这样,对于PTAT和VBE叠加的这个方法改变镜像电流的关系应该可以做到吧?

不好意思我没表述清楚,我的意思是可以得到任何你想要的电压,不仅仅是1.2V

何止啊现在TSMC 14nm已经搞定了苹果下代14nm工艺的A9订单将会被三星和TSMC平分······

14和16之间没有代差。下一代是9和7。

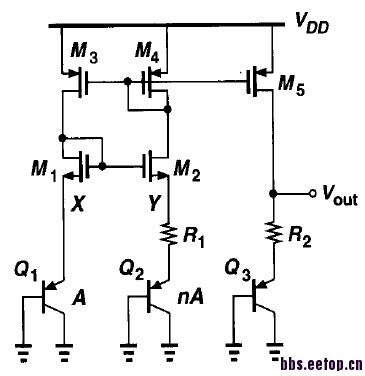

再问前辈一个问题PTAT电流支路下面的那个BJT个数怎么选?就1个吗?还是可以并联很多个?依据是什么?

你说的是什么结?

Q3的设计不是特别重要,主要考虑是mismatch和电流密度对BJT的温度特性影响。R1的大小就觉得了每一路的功耗。

您说得对R1决定每一路的电流大小也就决定了功耗但是我的疑问是R1该设计成多大合适呢?让每一路流过10u?20u?或者其他电流?我该怎么定这个值?查哪方面的东西?考虑到Q2的并联个数是N那么Q1的电流将会是Q2中单个管子的N倍单个支路电流和Q2并联个数的选择也有一定的原则吧? 请您从正向设计基准的角度给个指导您在工作中设计一个基准的时候是怎么考虑的?谢谢

R1 大所有电阻都大,但功耗小。R1小功耗就大。如果不在乎这些,就看看Q上的电流密度对其特性的影响,一般来说BJT电流密度太小那么Vbe稳定差,电阻Corner发生变化,引起的VBE变化大。另外BJT电流密度太小温度系数也不太好,并且噪声大。

您这里定性的说了一下BJT的VBE和电流密度特性我理解了但是我设计实际的电路“大”和“小”是要实际的数值我该查哪方面资料?foundry的PDK吗?spice模型?

仿真吧

foundry给你的doc里应该有bjt的测试数据和拟合曲线,可以先根据图表确定一个大致范围,避免仿真的时候太盲目。

一般mix cmos工艺里的bjt都是固定的单元,不支持自己更改e极面积,所以最小的电流是有个限度的,不然管子都打不开。

呵呵