对于带隙基准中运放和稳定性的一些问题

时间:10-02

整理:3721RD

点击:

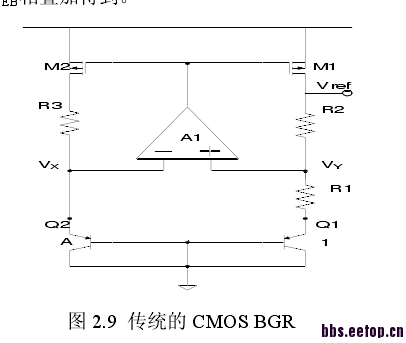

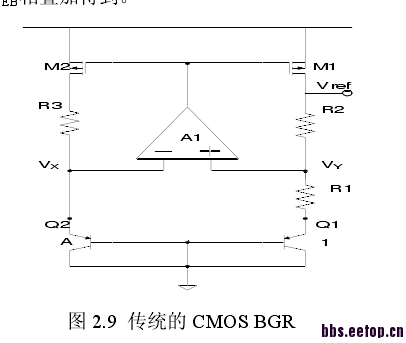

带隙基准中的运放采用二级运放的结构,电路图如下。二级运放可以通过电阻、电容密勒补偿的方法提高稳定性,很容易使运放的相位裕度大于60度。问题1:是运放稳定了带隙基准就能够满足负反馈并且稳定了么?个人感觉应该不是吧,因为运放输出端相连的PMOS管也是一级放大,有的时候仿真就发现虽然运放相位裕度够了,但是带隙输出电压还会震荡。问题2:对于这种二级运放为核心运放的带隙基准结构,需要怎么来进行补偿才能使基准的环路稳定呢?问题3:而且我看有一些文献中写道可以利用stb仿真来验证环路的稳定性,断开运放的输出端,并加入激励,具体应该怎么做呢?

1,不是,环路稳定不稳定要看整体。2,一般用一级运放。3,不用加激励,加个电压为0的电压源就可以了;网上有stb仿真设置。

cadence的操作手册里有关于STB仿真的说明的。不过我用的是hspice,所以帮不了你。