请教LDO流片之后的两个问题

1.load regulation比较差,随着load加大输出减小,0-1A掉了40mV@1Vout。并且在不同的Vin下掉的不一样,输入越高会有所改善,但是趋势没有变

2.line regulation在5V-6Vin下会突然变差,在2V-5Vin下几乎没有变化

希望做过LDO的大婶指导下小弟,要不没法过年了

呵呵,没法过年这说法太过分了,不至于。

1. 芯片有一个回路,一个输出级。输出的功率管那条线脚Power Line;反馈回内部EA的那条线脚Sense Line。这两条线虽然在电学原理上是同一根线,但是在Physics上,它们算两根线。Layout的时候,你需要做两个Bonding PADs,分别连到这两根线上。

2. 查查你的Vref,我估计是5~6V的时候你的Vref变了。更General点说,你的所有用Cascode架构的第二层的管子有可能有Drain-to-Sub的漏电。这个东西叫Impact Ionization。做这种工作电压高的电路,需要避免电流竞争,多用analog invertor的结构。

如果你还不理解就贴图吧,放心都是小Bug,不过没准需要Full Mask Change,不知会不会让你老板抓狂呵呵。

simulation结果是多少?

detail的performance问题,不贴电路没法看。

1只能看看你simulation的时候有没有加bonding的寄生电阻,如果只bond一根线,又比较长,30mo的电阻不是没可能,这样1A就30多mV没有了。大电流低输出电压,一般都会force sense的打线

第2个问题,如果simulation没有问题,建议看看pcm或者spice model的fitting曲线,看看是不是mos

在5v以上会有明显的上翘,如果是,关键的需要gain的地方,检查device的L,最好用cascode。另外,测试的负载是多少,如果负载重,也要考虑电压高,压差大,芯片内部温度过高

楼上2位有很深的造诣呀。

谢谢。有FB的pad。所以sense应该是没有问题的。另外您提到的可能原因我再看下,电路拷贝不了,所以抱歉了。

simulation没有问题,corner下也没有问题,谢谢您的建议,我再仔细查看下,我个人猜测可能layout方面有些问题,电路我拷贝不出来,因为公司内部的资料传不出来。非常感谢您的回复。新年快乐。

关于2,是用什么工艺实现的,如果是5V工艺,就是设计出了问题,如果是3.3V工艺,那么应该说不是什么大问题。要耐压只能采用Cascode结构

高手呀楼上的佩服

顶二楼三楼

设计时取样反馈要考虑寄生电阻的影响

如果测量的是没流过大电流的FB,那如楼上所说有可能是bandgap的问题,若bandgap有bypass引脚,可以先验证它的性能

学习了!

仅提供一点建议:对于第一个问题我觉得可以从Rdson、测试方式、版图的布局、基准的温度特性、以及失调等方面考虑,可以首先测试下你的Rdson多大?测试方式是否正确,尤其是输出端的连接方式是否正确?第三点版图的布局布线包括打线电阻,几根线是金线还是铜线?算一下实际的打线等效电阻是否跟仿真一致,功率管上的孔是否够多等,这都会也可能影响Rdson,不知道你的基准温度特性以及封装的散热特性如何?大电流下是否过热影响基准电压的漂移,失调这个可以从增益及匹配性上考虑,应该不会是这一点。

对于第二个问题应该跟你工艺的管子栅极耐压有关,最好跟工艺厂沟通下具体耐压如何?不知你是正向还是反向?如果换工艺了线性调整率的测试条件也要随工艺进行调整!希望能帮助到你!放假了人气确实低了点啊!

高人。 另外可以看看Supply的电流在高电压下是不是突然增加许多。

小编找到原因了吗?要反馈和分享哈?除了寄生外,你这两个问题都和环路增益有关,环路增益又于corner有关,你的环路增益是不是在某些与电压有关的corner下下降了呢?

反馈。

不明白为什么Vout和FB分别需要两个Bonding PAD,求解释

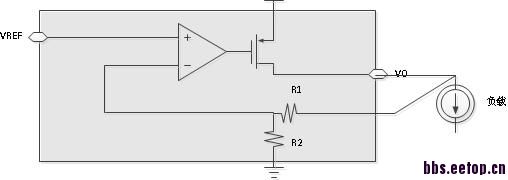

2楼不都说的很清楚了么……我来贴图吧,正确的接法是要那么接。不然VO那一整条wire的压降会影响到精度的。反馈只能保证sense端电压准确,也就是图里R1的上端,这点物理上要直接接负载的上端,或者接VO在PCB上的地方,因为PCB上电阻购小了

不过小编已经说了不是这个问题,坐等答案。小编记得回来啊!

顶起顶起顶起顶起

明白了,非常感谢!

感谢大家的关注,现在已经debug结束,第一个问题是因为内部有根GND线出现了PGND和AGND共用的情况;第二个问题是工艺上pmos的leakage比较大,导致offset随着电源会变大。已经改版流片验证成功。还是谢谢eetop上的xdjm们。

请教wind2000sp3, 您有提到:

"需要避免电流竞争,多用analog invertor的结构。"

请问analog inverter是什么?需要加在哪里?感谢。

就是共源放大器那种结构

学习了

学习了

请问PCM参数是什么意思,谢谢

看一看,学一学。

AGND,PGND有这么大影响?