运放失真

时间:10-02

整理:3721RD

点击:

在运放输入正弦波信号时若有1项之distortion,主要是由什么不足造成的?若有2项子distortion又是由什么不足造成的?

请牛人帮忙解释

请牛人帮忙解释

什么意思?没看懂……

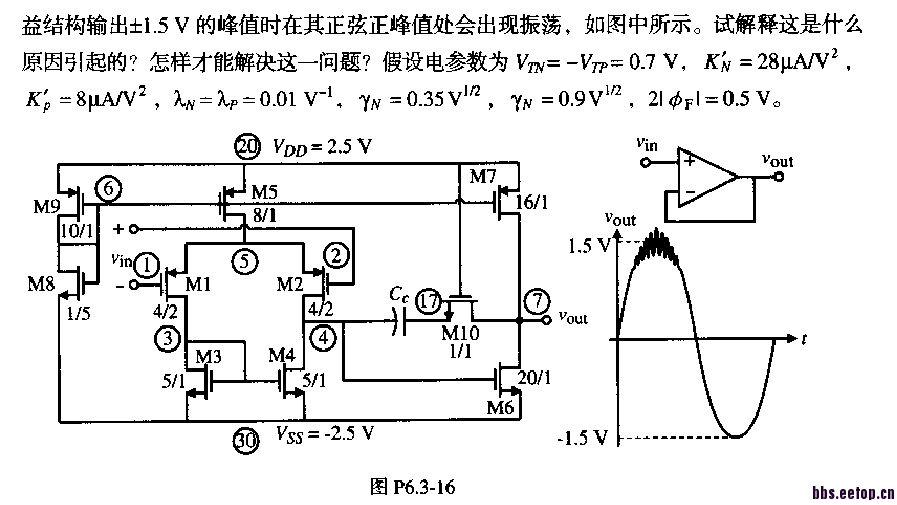

艾伦第六章课后习题6.3.16,,如下图。即有一处失真的情况。然后从之前师兄总结的面试问题中遇到了之间的题目

顶一下

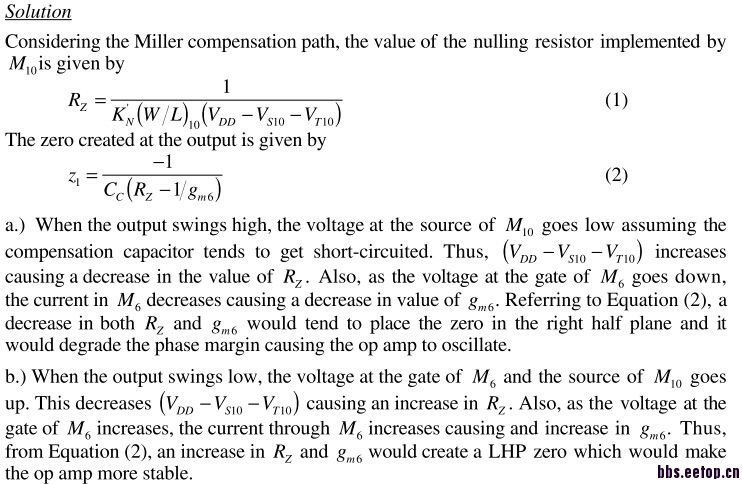

buffer大信号时,M6的电流减小,gm减小,同时M6 gate电压降低,M10的电阻也减小;RC补偿的零点和次级点都移动了

RZ减小,gm6减小导致了RHF 零点的移动,导致相位裕度不够。这是有一处失真的情况

那么会不会出现两处失真,也即不仅仅顶部失真也存在底部失真?这又是什么原因呢?

楼上的图是答案,小编可以参考下大神们也可以讨论讨论对不对

不是特别懂持续关注此贴 !

看一下1楼的题目嘛?我是有疑问的?

艾伦的课后题说的是一处失真的情况嘛,我还有一个问题的啊——出现两处失真是啥原因?

7楼的答案说的还挺清楚的,时域上的震荡,当然要从频域上的极点着手分析,但我觉得从摆幅角度应该也可以理解,由于是PMOS输入对管,因此,输入摆幅的上限需要仔细考虑,可以认为在输入信号达到峰值处时,M6栅极电压已经下降到无法使M6正常工作(即输出无法正常跟随输入),为了让M6在如此低的栅压下仍然能够平衡M7的下拉电流,需要加大M6的尺寸(以提高小过驱电压下的饱和电流),在偏置电流不变的情况也就是增大gm6.至于下峰值处为什么不失真,从这个摆幅的角度比较好理解了。

以上是从直觉上对这个电路的理解,无任何公式的推导,不妥之处请指正。