DC-DC中功率管和芯片是一个怎样的关系

时间:10-02

整理:3721RD

点击:

DC-DC中功率管和芯片是一个怎样的关系

功率管是外置的,那么芯片要达到怎样的要求才能够有效驱动功率管

大神们有相关文献么

功率管是外置的,那么芯片要达到怎样的要求才能够有效驱动功率管

大神们有相关文献么

Driver要驱动POWER MOS的Cgg,通常会有turn on速度的要求,不然efficiency会降低

谢谢你的解答,还有一部分表格

一个是驱动问题,还有一个是交叠问题

对于驱动功率管的功耗优化这方面有什么资料可以推荐吗

可以在论坛搜搜

这是在讨论什么,不是很懂。

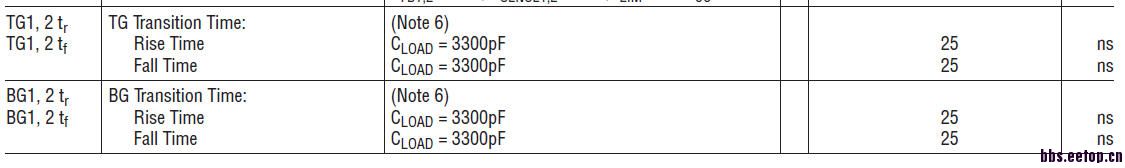

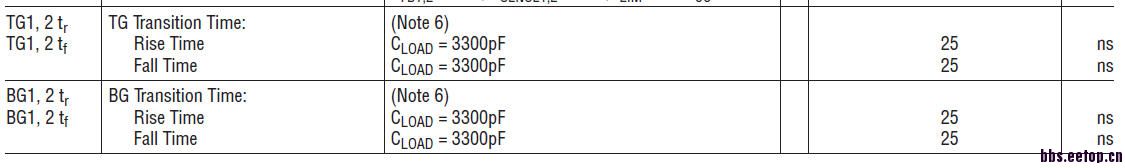

3L的图是driver中TG和BG的驱动能力,在Cload为所要求的值时,上升和下降时间所要达到的指标;

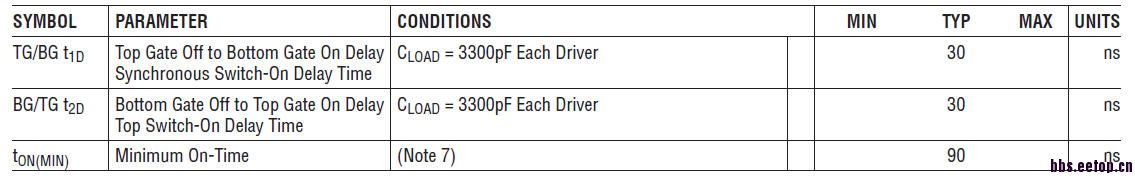

4L的图是driver电路的逻辑控制部分,保证TG和BG之间有dead time,防止TG和BG同时导通。

实际驱动MOSFET时,不同规格的MOSFET有不同的Ciss,如果drvier的驱动能力不足,MOSFET开启和关断的动作会很慢 。

谢谢你,有关于这方面比较好的资料推荐吗

还有一个问题麻烦你: 为什么高端管选用导通电阻小的管子,而低端管选用导通电阻大的管子。(输入电压小于20v)

有正向设计的功耗优化方法吗

考虑应用条件下的占空比,如果占空比小于50%,意味底部开关开启更久,所以会设计小点的导通电阻。