只用一个LDO,如何给数字电路和模拟电路供电?

时间:10-02

整理:3721RD

点击:

请教各位一个LDO应用的问题:只用一个LDO,如何给数字电路和模拟电路供电?

假设只有一个LDO(如TI的TPS717),输出需要接low ESR的1uF以上的电容。

这个LDO给数字电路和模拟电路供电,数字电源(DVDD)和模拟电源(AVDD)分别用1uF 耦合到DGND和AGND,同时AVDD和DVDD之间用一个小电阻/磁珠/电感串联,DGND和AGND之间用一个磁珠串联。

假设数字电路和模拟电路的平均功耗相等。

问题:

1)LDO的输出端是接AVDD还是DVDD?

2)由于LDO需要接Low ESR cap,说明应该是内部零点补偿了,那么数字电源和模拟电源之间的磁珠或者电阻与其中的一个输出电容是不是又形成了一个低频零点,导致LDO环路不稳定?

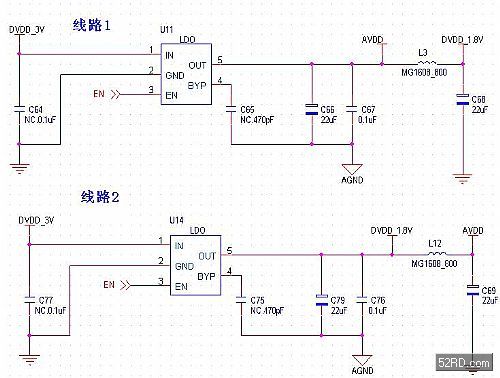

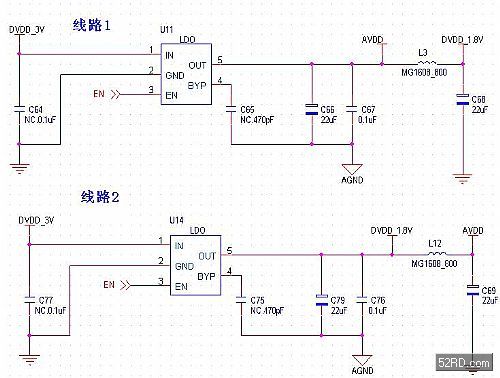

类型的电路如下图,原讨论帖在:http://www.52rd.com/bbs/Dispbbs.asp?BoardID=56&ID=73322

假设只有一个LDO(如TI的TPS717),输出需要接low ESR的1uF以上的电容。

这个LDO给数字电路和模拟电路供电,数字电源(DVDD)和模拟电源(AVDD)分别用1uF 耦合到DGND和AGND,同时AVDD和DVDD之间用一个小电阻/磁珠/电感串联,DGND和AGND之间用一个磁珠串联。

假设数字电路和模拟电路的平均功耗相等。

问题:

1)LDO的输出端是接AVDD还是DVDD?

2)由于LDO需要接Low ESR cap,说明应该是内部零点补偿了,那么数字电源和模拟电源之间的磁珠或者电阻与其中的一个输出电容是不是又形成了一个低频零点,导致LDO环路不稳定?

类型的电路如下图,原讨论帖在:http://www.52rd.com/bbs/Dispbbs.asp?BoardID=56&ID=73322

标题

自己顶一下帖吧,怕沉了。

个人觉得靠近LDO的输出端应该接一个较大的low ESR cap(如10uF),减小环路带宽(主极点内缩)。在靠近被供电的模拟电路的电源端接小电容(0.1uF),数字电源也是如此。将寄生的零点推往带外。

其次,LDO输出先给模拟电路供电,再经磁珠给数字电路供电。减少模拟电路的噪声。

不知道分析的对不对,还望大神指点

如果是PCB设计,应该是LDO输出两条线,分别接到AVDD和DVDD上,同时在AVDD和DVDD pin接近处加CAP。并且为了LDO的稳定,在LDO输出也应加Cap。

标题

我看到网上也有人这么说的,那么LDO输出端(Vout)的cap是不是要远大于AVDD, DVDD的那两个cap?如10uF和0.1uF

对,分开layout,加磁珠

滤除噪声是在DVDD和AVDD上的效果好,但要LDO上的 保证稳定