PLL中VCO设计的求助

时间:10-02

整理:3721RD

点击:

最近在做一个10MHZ左右的PLL时钟发生器(0.13um),我想请问一下VCO应该如何选择?

差分环形振荡器可以做么?但是感觉寄生电容相对较小,外加电容?有无这个必要?

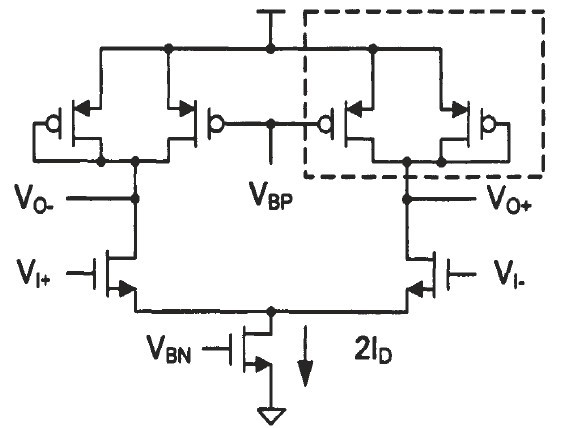

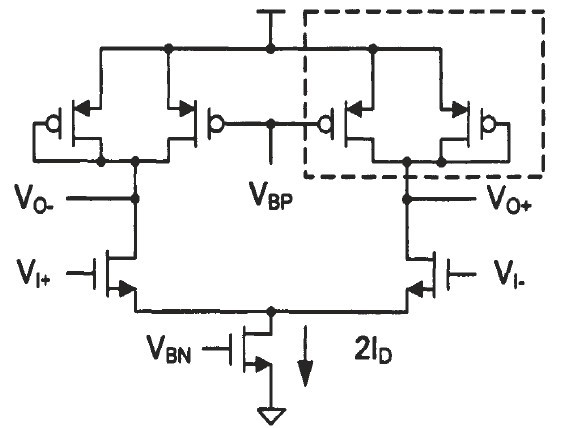

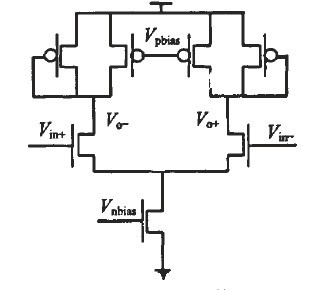

还有就是看对称负载的环形振荡器的振幅是VDD-VBP.那么在VIN=VDD时,VO=VBP,此时差分对管NMOS饱和会得出VBP≥VDD-VTN,负载

PMOS饱和会得出VBP≤VDD-VTP,是否有错?是NMOS不需要处在饱和区么?

谢谢!

差分环形振荡器可以做么?但是感觉寄生电容相对较小,外加电容?有无这个必要?

还有就是看对称负载的环形振荡器的振幅是VDD-VBP.那么在VIN=VDD时,VO=VBP,此时差分对管NMOS饱和会得出VBP≥VDD-VTN,负载

PMOS饱和会得出VBP≤VDD-VTP,是否有错?是NMOS不需要处在饱和区么?

谢谢!

10M 对管子要求不高的,寄生负载大一些就可以了,功耗也不会很大,可以做的很低

0.13um 设计10MHz,有点小材大用

恩,谢谢,是有点,不过导师要求0.13的,我看的paper都是GHZ的。如果要做的话,依靠寄生电容可以达到10MHZ么,我计算的时候感觉管子的W.L太大了,加个负载电容可行么。还有就是在VIN=VDD时,此时输出管子好像没法满足饱和状态?

SPEC 要求的就要做怎么能说大才小用呢。28nm也需要做32K的时钟呢。

VCO中的管子可以工作在线性区,但是电流源不能。用交叉耦合的VCO比较好,可以多用几级,电流小点,甚至加些cap,频率就下来了。

恩,谢谢你的意见,现在VCO基本设计好了,把各个管子的尺寸弄大了点,然后5级电路,最后加个整形电路,基本调好了。

整体功耗能做到多少?

你好,我最近也是刚刚做VCO,想请问一下你这个图的MOS管的宽长比是根据什么确定下来的?