相位裕度问题研究

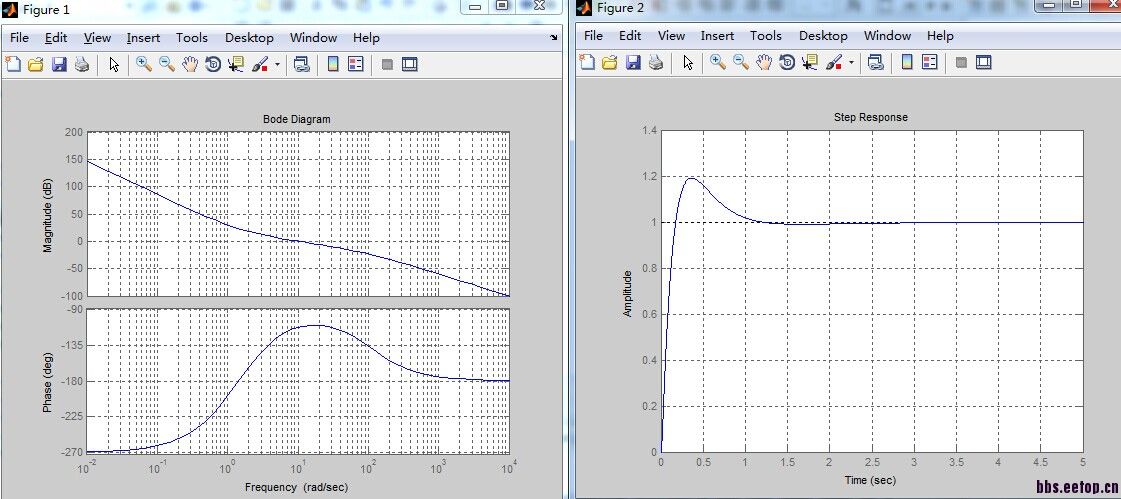

大家看看这个波特图和他的阶跃响应。

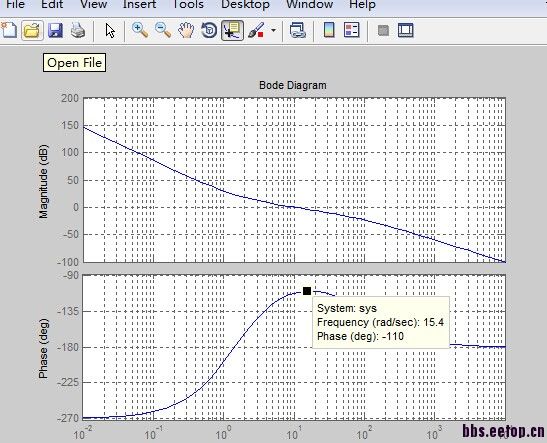

是不是很多人困惑到底这一种波特图的相位裕度是多少。这个图的phase margin是70度。

高频意味着响应速度快,优先决定系统响应。

附上代码,赶紧睡觉了。

num=[1000 3000 2000];den=[1 100 0 0 0];

sys=tf(num,den);

figure(1);

bode(sys);grid on;

figure(2);

numc=[1000 3000 2000 ];

denc=[1 100 1000 3000 2000];

c=tf(numc,denc);

t=0:1e-3:5;

step(c,t);

grid;补充下:发帖只是研究内容分享,补充教科书中不曾提及的问题。

赶紧睡觉

Phase margin 和step response 有点相关性,只能说有点

what‘s your point?你是想和教科书对比还是怎样?

is thispll responsing to frequency?

小编观点已经很明确了“高频意味着响应速度快,优先决定系统响应”

还有没听明白的么?

这个也可以解释条件稳定性的问题。

开环波特图可以直接反应阶跃响应。多环路系统不适用波特图,不是波特图和阶跃响应没关系。

No. There are 3 poles in zero.

没有,只是有人在论坛提出疑问。我研究了下。

这东西放在这有点白瞎了。

pm。

请教一下,如果一个电路里面有三个以上的环路,你们一般怎么仿真并判定每个环路的稳定性以及整个系统的稳定性的呢?有的时候采用sp1tswitch开关,断开每一个AC环路,似乎又不能把负载的寄生电容考虑进去。

STB仿真,仿真某个环路是其他环路闭环工作。如果保证每个环路稳定,那么系统肯定稳定,但这个不是必要条件。

波特图当然和step response 直接相关,但不是phase margin

建议把问题是什么,以及如何解决,写的更详细一点,否则容易看不懂,小编想表达的意思。

我估计他想说为什么70度phase margin还有20% overshoot,而且这种情况下,增加Ugb,牺牲phase margin应该有更好的顺态相应。其实这个根本就不是个问题,phase margin顶多能解释某些系统ringing的问题,至于oVershoot显然还和闭环零点有关。说到底现有模电教科书深度还不够。

顶了!下来看看。

好,以后注意。

其实这种波特图的稳定性可以通过梅森公式和根轨迹分析,肯定是稳定的。

意义不明

根轨迹分析理论上很完备,不过你们实际设计电路时,确实会使用根轨迹分析理论计算稳定性吗?这个和实际仿真吻合度如何?还是说根据开环的零极点位置的仿真的大致信息,估计闭环后,零极点的移动

numc=[1000 3000 2000 ];

denc=[1 100 1000 3000 2000];

c=tf(numc,denc);

你确定你代码没贴错?

就是需要小编这样的同志学习起来容易多了

没有

你BODE图明显三个0极点,可是你的代码没有。

num=[1000 3000 2000];den=[1 100 0 0 0];这个不是三个吗。C是close loop的。

知识点很赞