关于CMOS单级运放电路设计,有2个不懂的地方,求助

时间:10-02

整理:3721RD

点击:

1、主放大器采用PMOS管作为输入管,能获得较高的相位裕度。能说说为什么用PMOS能获得较高的相位裕度吗?

2、共源共栅管用NMOS管,这样可以提高主放大器的次极点频率。什么是次极点频率,为什么能提高它?

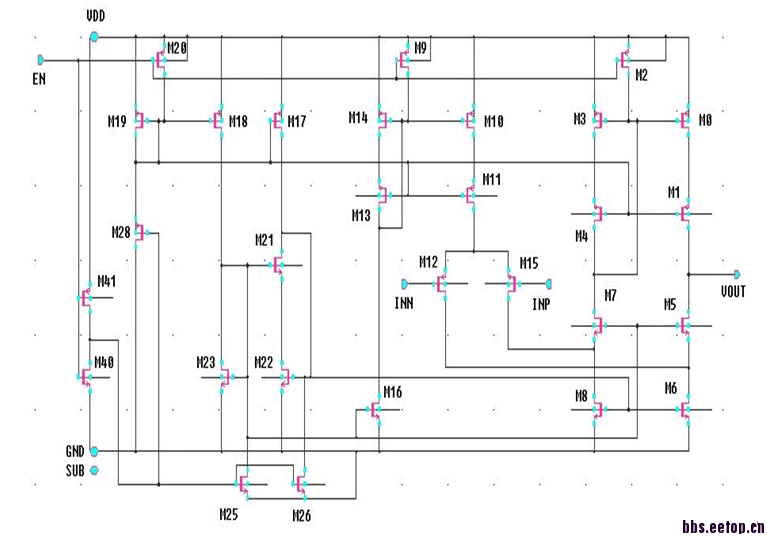

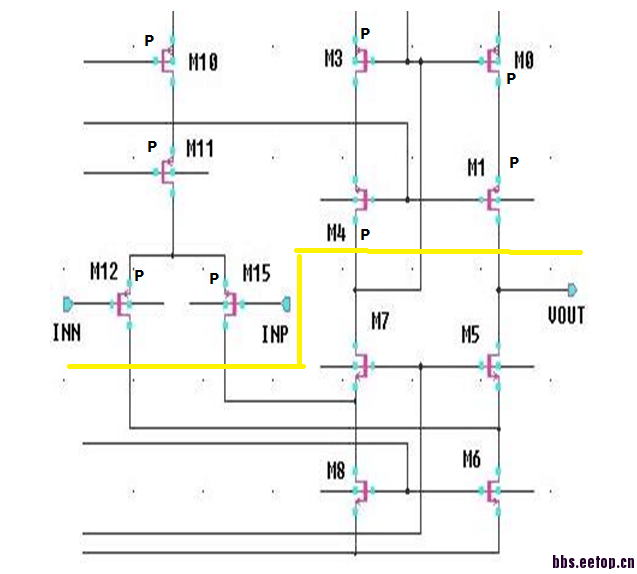

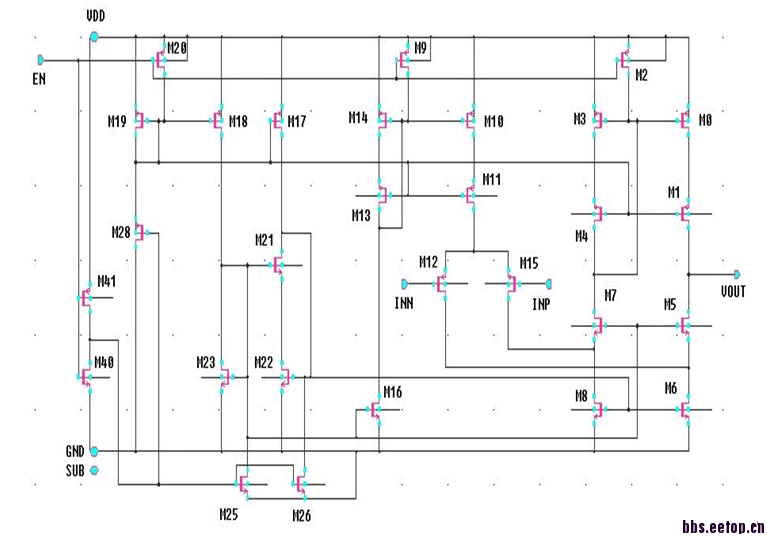

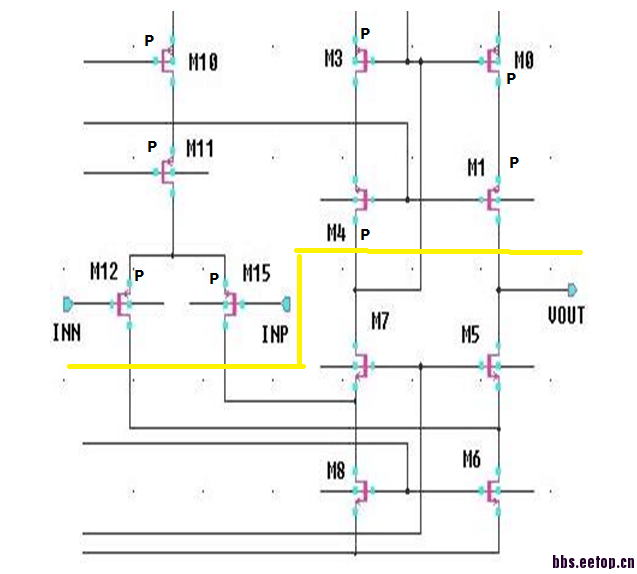

附上电路图,运放电路在右下角那一块,黄线是我自己画的

附上电路图,运放电路在右下角那一块,黄线是我自己画的

可能问题过于简单了,其实这是本人毕业设计的课题,我学的专业跟这个关系不大,所以不是很懂。麻烦各位高手解答一下,谢谢了

2、共源共栅管用NMOS管,这样可以提高主放大器的次极点频率。什么是次极点频率,为什么能提高它?

附上电路图,运放电路在右下角那一块,黄线是我自己画的

附上电路图,运放电路在右下角那一块,黄线是我自己画的

可能问题过于简单了,其实这是本人毕业设计的课题,我学的专业跟这个关系不大,所以不是很懂。麻烦各位高手解答一下,谢谢了

P管输入,只能N管求和了。P管 Gm小,带宽小有利于稳定。

感谢解答,大概懂了,我再去翻书找找公式。能回答下第二个问题吗,次级点频率是怎么回事?

次极点频率应该是指第一非主极点,对于折叠式运放,一般来说,第一主极点在输出端(RCL),第一非主极点在折叠点,图中M5,M6或者M7,M8之间的节点,它的大小为(ron7//ron8)*(C)的倒数,其中C为寄生电容和M7,M8,M12,M15的size有关,相比于PMOS,在相同情况下, NMOS的导通电阻小一些,所以第一非主极点被推高,一般情况下,为了保证电路的稳定性,第一非主极点会被推到单位增益带宽的2.2倍以上来保证60°相位裕度,所以这样做有利于提高相位裕度。

解释的很到位

其实这是本人毕业设计的课题,我学的专业跟这个关系不大?

为什么会这样呢?

手动赞

万分感谢!

我那个导师她说是想通过这个课题带动学院里这方面的技术,让我以后带学弟学妹。其实她自己也不是很懂这方面的知识,现在她也表示这课题难度太大了,不过没办法了,改不了。

对你的导师呵呵。

不客气,有问题可以加我Q(525333408)一起讨论,我也是刚入门

好的

看来大家都是新手,我建立一个群,新手共同成长的群。我们可以一起讨论。457214611

赞

我最近也在研究这个运放,连偏置都有点像啊不过我是电流源偏置

小编的运放增益和带宽分别是多少?带多大负载?用哪个工艺?

这中单端输出的运放,输出电压是怎么确定的?