请教:LDO对VCO噪声性能的影响如何消除

时间:10-02

整理:3721RD

点击:

LDO负载有一个1uF电容,连接到1G的VCO后发现VCO相位噪声下降了5-10dB,检查噪声贡献发现VCO噪声基本都来源于LDO,尤其是LDO的几个电流镜管子,我调整了管子尺寸之后可能某个管子的某个噪声降低了,但整体VCO噪声性能还是没有优化。想请教一下大家除了设计一个低噪声的LDO之外有什么办法能减小LDO对VCO噪声的影响呢?

比如在LDO和VCO连接的地方加一些滤波电路?电流镜栅极之类的地方加电容?不太懂这方面的内容,希望有经验的高手帮忙解决下呀

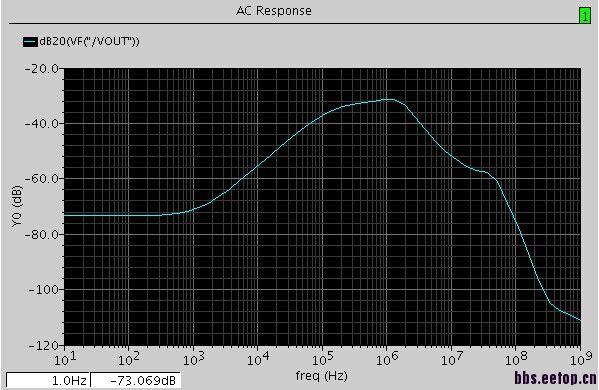

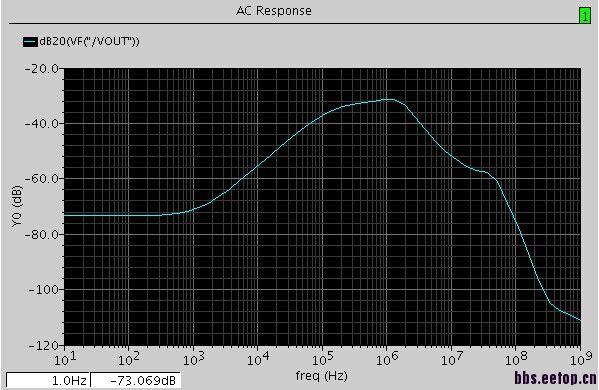

再就是下图是LDO的PSR曲线,想问下这个LDO的PSR性能对么,高频处下降这么多?

比如在LDO和VCO连接的地方加一些滤波电路?电流镜栅极之类的地方加电容?不太懂这方面的内容,希望有经验的高手帮忙解决下呀

再就是下图是LDO的PSR曲线,想问下这个LDO的PSR性能对么,高频处下降这么多?

LDO是供电方案中噪声很小的吧,总比DCDC强得多了

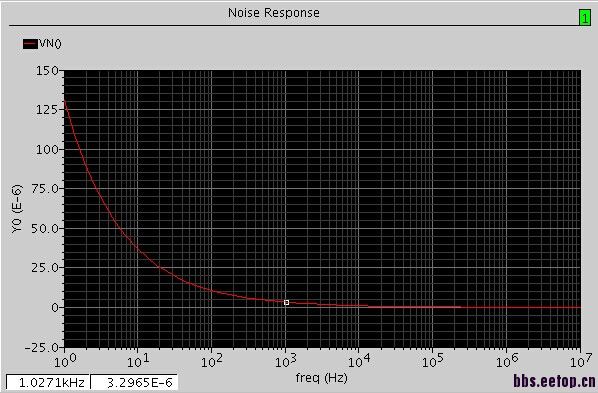

嗯,那我能做的只有尽可能降低LDO噪声了是么?之前对噪声没有什么概念,麻烦问下我这个输出噪声曲线是太大了么?

貌似这个噪声是大了些

我们稍大的电路也就100n数量级

不是特别在意低频噪声,看看PLL带宽处的。

片外电容没什么意义。

之前LDO的负载电容比较低,加到VCO上之后LDO输出会出现震荡,和VCO频率一样~后来才加大电容慢慢发现这个震荡没有了,但这电容太大片内也用不了了~还有什么更好的办法么?

有点震荡不是不稳定,没问题的,控制下幅度即可。

有点震荡不是不稳定,没问题的,控制下幅度即可。和VCO同频率的多噪声影响不大

嗯,确实是这样,之前发现过同频率的震荡,但仿真下来发现对VCO的性能却没有影响.但之前那个震荡幅度达到0.2V了,电源电压2.5V,这算可以接受的范围么?

add cap

太大了点,0.2V对VCO有影响了吧。这个震荡可能影响别的电路。

我这边做了一个26MHz crystal,单独做了一个无电容LDO给其供电,联仿发现 电源上会出现较大的pp抖动,将近300mV(1.2V)电源电压,这样导致Crystal出来的方波高电位不是平的,而是曲线,这样会不会出问题啊

应用到VCO的LDO需要特殊设计低噪声,rms没有10uV量级都不好意思拿出来用的

有啥好的建议或者参考paper吗?

回复 2# semico_ljj

应用到VCO的LDO需要特殊设计低噪声,rms没有10uV量级都不好意思拿出来用的

这个要求很高啊,10uV,肯定要片外的大电容的。