拉闸维书上的问题(关于源级跟随器)

时间:10-02

整理:3721RD

点击:

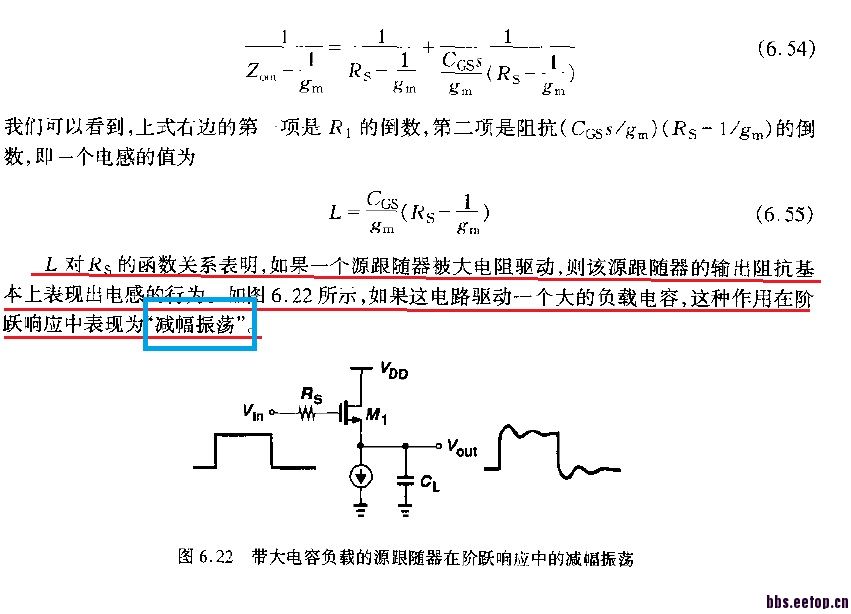

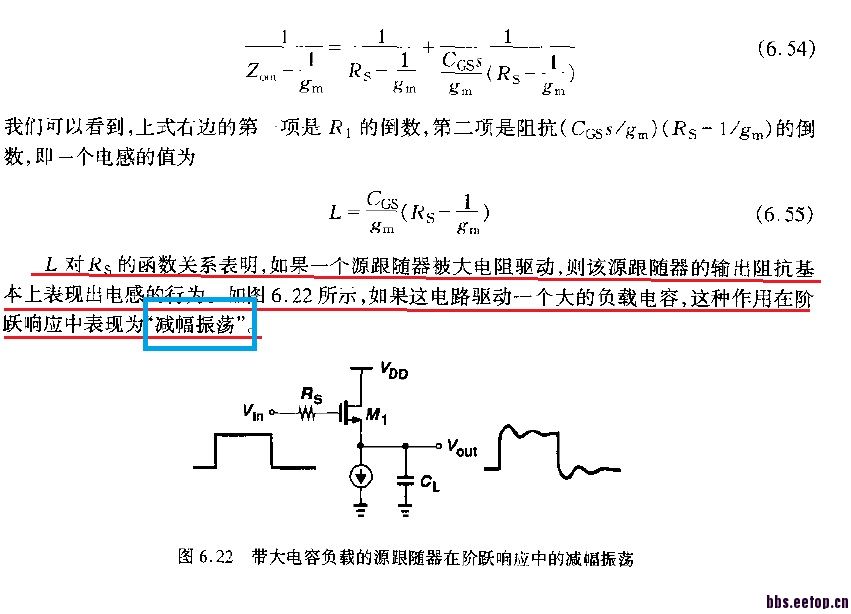

拉闸维第六章关于源级跟随器的输出阻抗问题中有如图所示的阐述,特别不能够理解,希望有大神解之。

书中所说的源级跟随器输出阻抗表现为一个电感,驱动一个大电容情况时,若是阶跃响应,输出会表现出“减幅震荡”,应该如何去理解啊?

谢谢你们的宝贵意见。

书中所说的源级跟随器输出阻抗表现为一个电感,驱动一个大电容情况时,若是阶跃响应,输出会表现出“减幅震荡”,应该如何去理解啊?

谢谢你们的宝贵意见。

顶一个...

有人可以具体地解释一下吗?多谢多谢。明天答辩。

大电阻引入一个很低的输入极点,导致系统的稳定性变差,在输出看到的就是减幅震荡

和电感有何关联?

我也不懂。最近也在看拉扎维。同问。求大神指点

我觉得是因为这里引入了一对复极点对,复极点对在阶跃响应时,虚部即是震荡频率,实部即是衰减系数

如何理解你所说的引入了复极点对?如何推倒出来的?

你可以尝试用头脑模拟一下。

对于这种gate串了大电阻的source follower。如果你在vout端以很缓慢速度的抽电流。这种低频条件下,gate能稳定在vin,所以MOS能提供得了电流能力,从vout端看进去的输出阻抗较低。

但如果你以很快的频率抽电流,比如一个阶跃,首先VOUT会掉下来,由于rs的存在,很容易通过M1 CGS把M1的gate couple下来,也就是VGS几乎不变,MOS提供不了电流能力。所以高频时从vout端看进去的输出阻抗较高。

总结一下,对于gate串了大电阻的source follower,输出阻抗随着频率增加而增加,和电感是一样的特点,因此。从vout端看进去呈现电感的特点。

想图中所示的情况vout自然就会有震荡,那是LC结构的特点。

我想说的是source follower也是有频率响应的,“输出阻抗低”是有条件的。弄得不好也是会震荡的。

这个解释很形象,学习了

谢谢你的解释&帮助

9楼大神啊

你可以用负反馈来理解