LDO的瞬态响应问题

是问题太简单了吗,没人回答哎

我也想知道答案,求大神指点

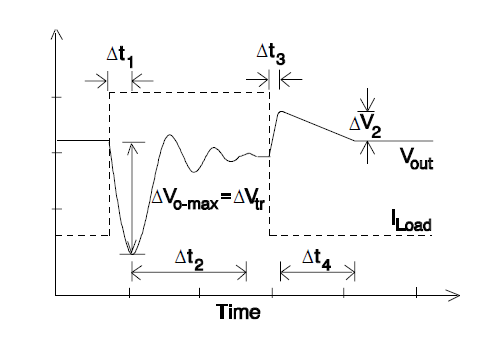

t1是大信号响应,t2是小信号响应

细致的分析不解

大信号跟闭环带宽有什么关系呢,闭环带宽难道是大信号的衡量吗

t1主要决定于摆率吧?

摆率跟闭环带宽有什么关系呢

我觉得t2的时间与闭环的带宽是有关系的,类似于给你的闭环环路加了一个单位阶跃。闭环的响应还与稳定性有关(开环相位),你可以看出那幅图有ringing。t1时间的响应和voltage spike的产生很复杂,除了环路的slew rate,还与负载电容大小和负载电流的下降沿都有关系,很难定量分析。基本就是定性了解就可以了。

t1主要是摆率决定,摆到LDO稳压区时,剩下的时间由UBW决定

gdjack 说得对

这跟闭环加阶跃响应还是不同,我觉得闭环阶跃是跟随的效果,这里可以先过冲再拉回来哦,其实我觉得t1时间内环路已经有所动作,环路已经开始抵制外力的作用,类似刚开始刹车,车速虽降下去,但方向还是没有变,t1结束时环路响应的程度好比使车停了下来,然后就是倒车了,而倒车的过程类似于环路重新建立新的稳态的过程

继续等大牛分析

t1 主要由摆率吗?如果摆率无穷大,就没有负向冲了吗,此时瞬态波形会是什么样呢?我相信即使摆率无穷大,负载跳变时,输出还是会变化,

因为过了摆率就是闭环响应了,此有限带宽来拉住下冲的趋势? 我想可能是这样吧

坐等大牛解释

等高手解释哈,

我觉得t2环路重新建立的过程可以用闭环响应来“近似”,不过很难精准描述。你说得对,t1的时候环路已经开始有作用,不过这时反馈的环路是的断开的,这时的LDO都不是一个线性的反馈系统。t1和t2的分界就是LDO的电流输出I_out=负载电流I_load,输出电容I_cap=0,之后环路开始对电容充电,使Vout回到正常值,这个t2的过程个人觉得可以看成是线性反馈系统。

t1的过程中,重要的是I_out的增加,基本上是power transistor的gate端在slew,导致I_out增加,在t1的末尾,gate端的slew结束,线性反馈环路开始逐渐起作用。不过究竟什么时候线性反馈开始起作用,我想是非常难定义的。

欢迎讨论啊 我认为t1过程中 ldo必然有一段时间是线性的,但是这线性不足以满足负载的要求,所以输出电压还会继续下掉

我想t1和t2的分界点不是线性和非线性的分界处,而是在经过t1内部一段时间的线性后,使得ldo输出满足了负载的要求,从而输出不会往下掉,再经过一段时间t2 重新建立稳态

欢迎讨论哦 谢谢

t1大信号,t2小信号响应跟LDO带宽有关。

能否讲讲理由 ,别只是给出结论

之前感觉热心的高手很多哎

现在他们都不混论坛了?

算了,我也放弃了

LZ推荐你看下莫拉的一本关于LDO的书。看后你就会明白。

本人刚入门,谈下自己的浅见。首先可以肯定的是,前面一段是由于输出电容对负载电流的增大而放电所造成,而至于后面的是不是由于小信号,本人认为是关系到最低电压是不是在运放的输入范围之内等其他因素,但是可以肯定的是,后面那一段小信号肯定会造成rings