带隙中的偏置的问题

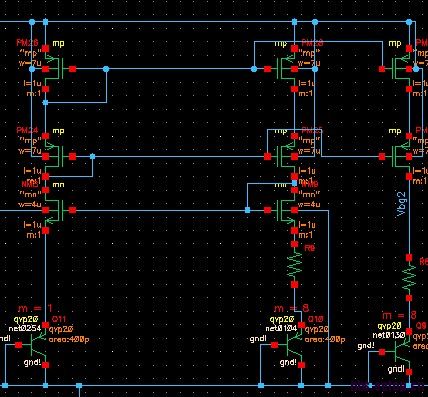

图1

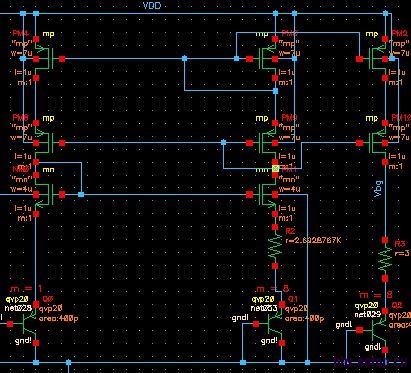

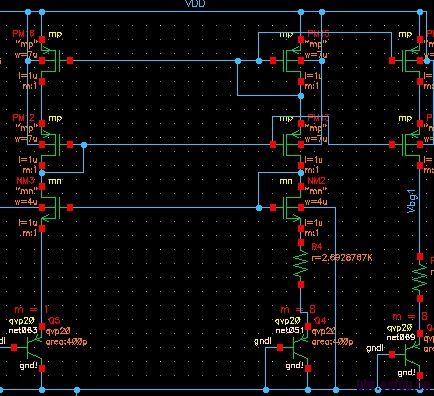

图1 图2

图2这两个区别

把中间那级偏置管MP8MP9先去掉不就很明显了啊

有个图画错了

只有图2正确,其余两个都不对。从PTAT自偏置电路的两个NMOS管的源端分析环路节点极性,配合高低阻节点匹配设计,可以判断出来。另外,L取的太小,参数也不匹配,最好改用低压PMOS电流镜,输出支路Q管取1就可以啦,取8太大,版图不好匹配,能用qvp10就不要用qvp20的,太占面积,电阻用负温度系数多晶高阻,没见显示model类型~

图2是三张图里面唯一正确的。不过我觉得M8和M9的栅两边都可以接,甚至接到其他偏置也是可行的,因为他们是用来给上面两个P mirror做cascade的。另外,小编用来做mirror的P管栅长取的太小了,怎么也不得来个20u/40u的。

谢谢

从PTAT自偏置电路的两个NMOS管的源端分析环路节点极性,配合高低阻节点匹配设计,可以判断出来。不是很明白啊

另外1.因为我用的是.35的工艺,以为mos管的L取1u已经够大了,

2. 你说的参数不匹配?是指nmos和pmos的W/L不一致吗?如果是这个的话,因为nmos和pmos的迁移率不一样,所以我弄的W/L不一致

3. 别人跟我说过bjt的面积越大,则它的匹配性越好,所以我选了qvp20,

4. 电阻的model是用高阻的负温度系数的poly

谢谢请指正

不知道你之前是做什么的,感觉没入门...

知道bjt的size 要取得大,却不知道mos的size也要取大

找本书认真看一看

什么是高低阻节点匹配设计?我以为图1是正反馈所以错了,图3没没有反馈所以错了。

.35工艺用30、40栅长的管子很正常,电流镜匹配好嘛。

谢谢 关注

30、40栅长的管子,尽管电流镜匹配很好,但是它的flick noise不是会变得很大吗

对的,这就是这个结构限制的,必须在电压精度和噪声之间做一个trade off

Flick noise不是和面积呈反比吗?栅长变大噪声会变才对啊?为什么说需要在电压精度和噪声之间trade off呢?

什么叫高低阻节点匹配设计?

查了一下书,确实闪烁噪声跟面积呈反比,谢谢你的指正。

你好,我想请问一下qvp5 qvp10有什么区别呢