PLL输出相位噪声到抖动的转化

时间:10-02

整理:3721RD

点击:

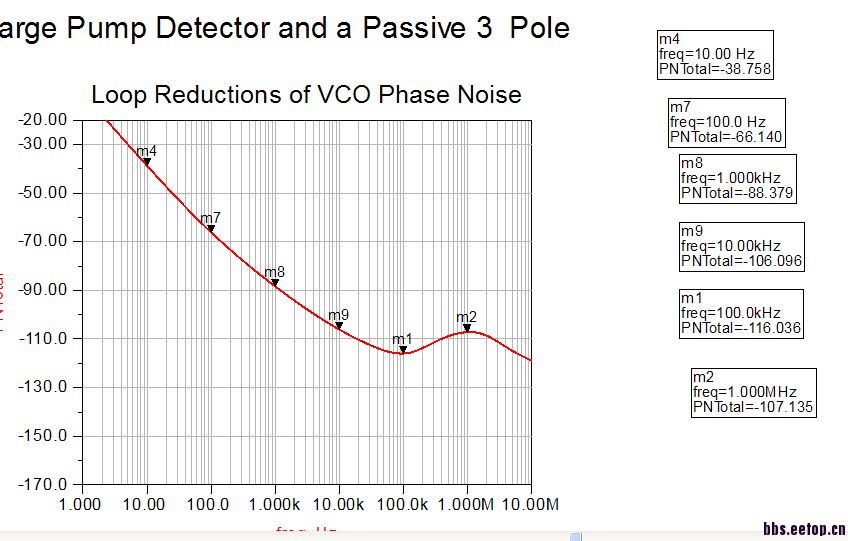

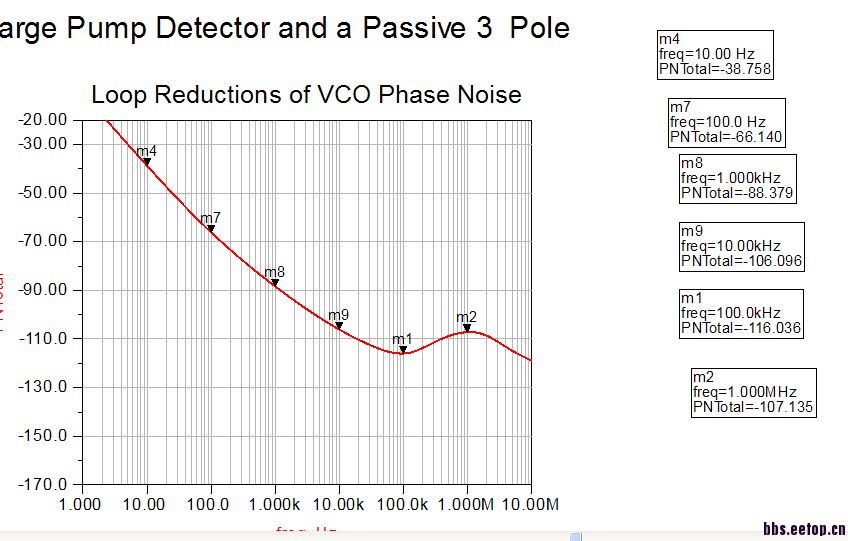

仿真得到了PLL输出相位噪声,如下图,因为做的是时钟信号发生器,所以要把它给转化为抖动,周期抖动的RMS值,但一直有一个疑惑:这个曲线的频域积分的频率积分范围到底应该怎么选?听说做时钟发生器和频率合成器都是带内积分,但是为什么呢?还说有一些应用需要在某个特定的频率范围内积分得到抖动值?我一直搞不懂为什么?还请高人大神指教!

你把横坐标换成linear,纵坐标换成绝对值,就会发现。

其实一定频率外后相位噪声面积很小了。

理论上肯定是积分到无穷大,但其实积分到fref频率的RMS值和积分到无穷大的值,差不多

谢谢您的回复,做时钟不是积分到环路带宽处就可以了吗?怎么是参考频率Fref呢? 这个搞不懂,还请大神指教

积分值应该差不了太多,你可以实际看一下,理论是积分到无穷大

好的,我去试一下,谢谢大神

gdfggdfgdfgdfgdfg

积分到1/2的所测的时钟频率

谢谢您的回复,您说的所测的时钟频率指的是参考频率还是PLL输出频率呢?若是输出频率300M,那岂不是得从0积分到150M?

是的,高频到1/2 target frequency,低频不可能取到0,你想要pll工作一万年?

呵呵,谢谢大神指点,低频从10Hz开始吧

算完之后需要乘以2吗?

仿真器给出的PN曲线,已经是单边带了呀